**Reactive TestBench**

**Generation Option**

# **User's Manual**

www.syncad.com

# Reactive TestBench Generation Option User's Manual (rev 10.0) copyright 1994-2005 SynaptiCAD

Trademarks

- Timing Diagrammer Pro, WaveFormer Pro, TestBencher Pro, VeriLogger Pro, DataSheet Pro, BugHunter Pro, Reactive TestBench Generation Option and SynaptiCAD are trademarks of SynaptiCAD Inc.

- VERA, OpenVera, VCS, and VCSi are trademarks of Sysnopsys, Inc.

- NC Verilog, NC VHDL, and Verilog-XL are trademarks of Cadence Design Systems, Inc.

- Pod-A-Lyzer is a trademark of Boulder Creek Engineering.

- PeakVHDL and PeakFPGA are trademarks of Accolade Design Automation Inc.

- V-System and ModelSim are trademarks of Model Technology Incorporated.

- Viewlogic, Workview, and Viewsim are registered trademarks of Viewlogic Inc.

- HP and Agilent are trademarks of Hewlett Packard.

- Tektronix copyright Tektronix, Inc.

- PI-2005 and PI-Pat are trademarks of Pulse Instruments.

- Timing Designer and Chronology are registered trademarks of Chronology Corp.

- DesignWorks is a trademark of Capilano Computing.

- Mentor and QuickSim II are registered trademarks of Mentor Graphics Inc.

- OrCAD is a registered trademark of OrCAD.

- PSpice is a registered trademark of MicroSim.

- Windows, Windows NT, and Windows 95/98/2000 are registered trademarks of Microsoft.

All other brand and product names are the trademarks of their respective holders.

Information in this documentation is subject to change without notice and does not represent a commitment on the part of SynaptiCAD. Not all functions listed in manual apply to Timing Diagrammer Pro, WaveFormer Pro, DataSheet Pro, or VeriLogger Pro. The software and associated documentation is provided under a license agreement and is the property of SynaptiCAD. Copying the software in violation of Federal Copyright Law is a criminal offense. Violators will be prosecuted to the full extent of the law.

No part of this document may be reproduced or transmitted in any manner or by any means, electronic or mechanical, including photocopying and recording, for any purpose without the written permission of SynaptiCAD.

For latest product information and updates contact SynaptiCAD at:

web site: http://www.syncad.com email: sales@syncad.com phone: (540)953-3390

# **Table of Contents**

| Table of Contents                                                                                                                                                                                                                                                                  | 3                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Introduction                                                                                                                                                                                                                                                                       | 5                                      |

| Introduction<br>Chapter 1: Waveforms and Signals                                                                                                                                                                                                                                   | <b>7 7 8 9 9 10 11 11 13 14 14</b>     |

| Chapter 2: Delays, Setups and Holds                                                                                                                                                                                                                                                | 19                                     |

| <ul> <li>2.1 Adding and Editing Parameters</li> <li>2.2 Delays</li> <li>2.3 Resolving Multiple Delays</li> <li>2.4 Setups and Holds</li> </ul>                                                                                                                                     | 20<br>21<br>22                         |

| Chapter 3: Samples                                                                                                                                                                                                                                                                 |                                        |

| <ul> <li>3.1 Adding a New Sample</li></ul>                                                                                                                                                                                                                                         | 24<br>26<br>27<br>28                   |

| Chapter 4: Markers                                                                                                                                                                                                                                                                 |                                        |

| <ul> <li>4.1 Adding a Marker to a Diagram</li> <li>4.2 End Diagram Markers</li> <li>4.3 Loop Markers</li> <li>4.4 HDL Code Markers</li> <li>4.5 Wait Until Marker</li> <li>4.6 Pause Simulation Marker (Verilog Only)</li> <li>4.7 Documentation and Time Break Markers</li> </ul> | 31<br>32<br>32<br>34<br>34<br>34<br>35 |

| Chapter 5: Variables and Class Methods                                                                                                                                                                                                                                             |                                        |

| <ul><li>5.1 Variables</li><li>5.2 Class Methods</li><li>5.3 Language Independent Types</li></ul>                                                                                                                                                                                   |                                        |

| Chapter 6: Test Bench Techniques                                                                                                                                                                                                                                                   | 43                                     |

| <ul><li>6.1 Testing a Counter Model</li><li>6.2 Waiting for Signal Transitions</li></ul>                                                                                                                                                                                           |                                        |

| Index                                                                                                                                                                                                                                                                              | 45                                     |

# Introduction

The Reactive Test Bench Generation Option bridges the gap between the stimulus waveform test benches that are native to most of the SynaptiCAD product line and the bus-functional model generation of TestBencher Pro. This option allows users to describe single timing diagram test benches that react to the model under test and generate pass/fail reports. The Reactive Test Bench Generation Option can be added to WaveFormer Pro, WaveFormer Lite, DataSheet Pro, VeriLogger Pro, and BugHunter Pro.

With "Reactive Test Bench Generation" users have the option of drawing "expected" waveforms on the MUT output ports and adding "samples" to the waveforms to test for specific cases. During simulation the code generated by the samples would watch the output from the model under test and compare it to drawn states. The samples can perform a variety of functions such as pausing the simulation to debug a problem, reporting errors and warnings, user-defined actions, and triggering other samples.

The Reactive Test Bench Generation also includes markers that can be used to wait for activity from the model under test and/or loop over a section of a diagram. Markers can also be used to call user-written HDL functions ands tasks from within a diagram.

Reactive test bench generation also allows the option of creating "clock-based" test benches as well as the "time-based" test benches currently supported by the stimulus based generation models. Clock-based test benches delay in clock cycles instead of times, allowing the user to change his clock frequency without needing to change his timing diagram. Clock-based test benches are also required when testing using high-speed "cycle-based" simulators.

6 Introduction

# **Chapter 1: Waveforms and Signals**

Signals and waveforms are the heart of the timing diagram. The waveforms can be quickly sketched using the built-in timing diagram editor. The state values of waveforms can be hard coded. In TestBencher, state values can also be passed into waveforms through a variable, or conditionally driven by a variable.

Most of the signals will be automatically added to the timing diagrams by extracting the signal and port information from the model under test files. However signals can be added manually. Several types of signals including internal and clock signals can be added to the timing diagram to achieve different behaviors.

The edges on waveforms are responsible for triggering the markers and parameters that are attached to them. If more than one parameter or marker is attached to the same edge then triggering order can be set using the *Edge Properties* dialog. Also, edges of a can be made sensitive so that the transaction will wait for that particular edge to occur.

#### **Generation of Reactive HDL Code**

The Reactive Export feature (included in TestBencher Pro and optionally in other products) includes the generation of Boolean Equations with delays, registers, latched signals and behavioral Verilog code. Boolean equations and registered logic are useful for modeling interface glue logic that is not part of the model under test itself. The equations are entered through the Logic Wizard section of the Signal Properties, which can be reached by double-clicking on a signal name. Sections *12.1 Boolean Equations*, *12.2 Advanced Gate Representation* and *12.3 Register and Latch Equations* discuss the methods useful for generating interface glue-logic in a reactive test bench.

# 1.1 Drawing Waveforms and Bi-Directional Signals

The timing diagram editor is always in drawing mode. Waveforms are sketched by clicking the mouse button in the diagram window. The state buttons control which type of waveforms will be drawn next. The state buttons are the buttons with the waveforms drawn on their face: HIGH, LOW, TRIstate, VALid, INValid, WHI weak high, and WLO weak low. When a state button is activated, it is pushed in and colored red. The active state will be the type of waveform that is drawn next. Waveforms can also be edited by dragging and dropping edges, and by selecting segments and choosing another waveform state. The Timing Diagram Editor on-line manual provides in-depth information for the drawing environment.

# To Draw a Waveform:

- Click the type of state that you want to add in the group of 7 states on the right side of the Signal Button Bar.

- Click in the waveform section of the *Diagram* window to the right of the signal or bus name at the approximate time that you want the state transition to occur. This will place the transition in the waveform. Waveforms are built from left to right.

- Repeat the first two steps until you have completed the signal's waveform.

Signals with a direction of **output** or **internal** have black waveforms, and signals with a direction of **input** have blue waveforms. Bi-directional signals with a direction of **inout** will be drawn with mixed black and blue segments to indicate which segments will be driven by the transaction and which are inputs to the transaction.

By default all of the waveform segments on a bi-directional signals signal are assumed to have a direction of output and are colored black to indicate their direction. To change a segment to be an input segment (un-driven):

- Double-click on the input segment. This opens the *Edit Bus State* dialog.

- Uncheck the **Driven** check box. This indicates that the test bench does not drive this segment; this segment will be an input to the test bench.

- Click **OK** to close the dialog or use **<Alt>-N** or **<Alt>-P** (or the **Next** or **Previous** buttons) to edit other segments on the same signal. The segment for which you unchecked the driven flag should now be colored blue.

# 1.2 Driving Waveform States with Variables

Waveforms are normally driven to the drawn graphical state (high, low, tri-state, weak-high, and weak-low). However, waveforms with a graphical state of **valid** need to be driven to a distinct value during simulation. Using the *Edit Bus State* dialog you can hard code in a value, choose an existing variable in the timing diagram to drive the state, or in TestBencher define a state variable. If a waveform segment is drawn with a graphical state other than **valid**, that graphical state will be used to drive the signal and any other state information entered through the *Edit Bus State* dialog will be ignored.

In TestBencher, using variables to drive waveform states allows new values to be passed into the transaction each time it is called. This is convenient for timing diagrams that have data and address buses because each time the diagram is called new values can be passed into the timing diagram. **State variables** and **Diagram-level variables** can be used to drive a waveform state (see section *3.3: Transaction Level Variables* of the TestBencher Manual). Parameter based variables should not be used to drive waveform states because their type is fixed to hold time values not state values.

TestBencher state variables can be quickly defined in the *Edit Bus State* dialog by typing in a variable name that begins with two dollar signs like *\$\$addr*. State variables are automatically added to the parameter list for the transaction call. The type and size for these variables are determined by the signal that is being driven. Each time the transaction is called, a new state value can be passed into the variable. The same state variable can also be used on several signals and the maximum size will be determined by the min and max of all of the signals used. For example \$\$addr apears in SIG0[3:0] and SIG1[12:9], then the \$\$addr will have a size of [12:0].

Both TestBencher and the Reactive TestBench option support Diagram-level variables. The type and size are controlled by the user during the declaration of the variables. so they require a little more setup work (see *Section 3.3 Transaction Level Variables* of the TestBencher Manual). Also diagram-level variables can be conditionally driven by different sources like samples and signal states within the timing diagram during simulation as well as being passed into diagram.

#### To edit the state of a valid signal segment:

- Double-click on the segment of the signal to open the *Edit Bus State* dialog.

- The Virtual edit box accepts values, variables, and Boolean equations that meet the format shown in *Appendix C: Language Independent Operators*. For example, \$\$addr+@increment is an acceptable equation for the Virtual edit box.

| Edit Bus State      |   | _ 🗆 🗵    |

|---------------------|---|----------|

| Virtual: \$\$addr   | > | Variable |

| Radix: hex(default) |   | •        |

- To hard code a value, type the value in the Virtual edit box.

- To add a state variable, type the variable name using a \$\$ prefix into the Virtual edit box. For example,

*\$\$data* might be the name of the variable for the value of data bus. This variable will appear in the timing diagrams apply call.

- To add a diagram-level variable:

- Click the Variables button to open the *Select Variables* dialog. Double-click on the variable and click **OK** to close the dialog. The variable name with a @ prefix will be added to the Virtual box.

- OR

- Click the Variables Menu Button 🚬 to display a list of variables that can be inserted into the equation.

- Click OK to close the dialog box.

Note: State values can also be conditionally driven using the *Condition Tree* in the bottom of the *Edit Bus State* dialog. For more information see *Section 1.3: Driving Conditional State Values*.

# **1.3 Driving Conditional State Values**

State values can be conditionally driven based on events and states that occur during simulation. The *Edit Bus State* dialog contains a *Condition Tree* that can be used to build conditional strings for the state value. If the state tree is not modified, the value will be unconditionally driven to the value in the **Virtual** edit box. The driven state can be made conditional by adding a condition to the State Condition tree.

#### To create a conditional drive for the state value:

- Double-click the segment that is to be conditionally driven to open the *Edit Bus State* dialog.

- Right-click on the **If** row and choose **Add Condition** from the context menu to open an edit box or double click in the **Condition/Action** column of the **If** row.

- Type the text for the condition. The condition must be written in the generated language of the transaction and it must equate to a Boolean equation when evaluated during simulation.

| Edit Bus State                       |                                 |

|--------------------------------------|---------------------------------|

| Virtual: \$\$addr<br>Radix: hex(defa | Variable                        |

| ConditionTree                        | Condition/Action                |

| □ If                                 | TRUE                            |

| Then                                 | \$\$addr                        |

| Else                                 |                                 |

|                                      |                                 |

|                                      |                                 |

|                                      |                                 |

|                                      |                                 |

|                                      |                                 |

| -                                    |                                 |

|                                      | Driven (for inout signals only) |

| <=                                   | Prev OK Mext =>                 |

- Next, add the state values to the **Then** or **Else** rows by right-clicking choosing **Add Variable** or **Add State** menu option. Or double-click in the **Condition/Action** column and edit the state.

- Optional: Complex conditionals can be created using the Add If...Then...Else context menu. This option is available for any existing Then or Else row. Selecting this option causes a nested If...Then...Else to be added to the branch of tree that was selected.

| Condition Tree | Condition/Action |

|----------------|------------------|

| 🗆 lf           | ADDR === 'hF0    |

| — Then         | \$\$addr         |

| Ė–Else If      | ADDR === 'hAE    |

| - Then         | 'h1              |

| Else           | 'h0              |

|                |                  |

# 1.4 Adding Signals

Most signals will be automatically added by extracting the signal information from the model under test using the techniques that are discussed in *Section 3.2 Extracting MUT Ports into a Timing Diagram* of the TestBencher manual. Signals can also be added manually by using the buttons on the *Signal Button Bar*. Certain types of signals like compare and internal signals are always added manually.

The generated bus-functional model can provide stimulus and monitor simulation outputs of the circuit that you are designing. In order to do this, the signals that will be exported by the bus-functional model have to match the signals that exist in your designs. If the signals in the timing diagrams are named the same as in your circuit model then the matching will be automatic. If the signal names do not match you will have to create a sub-project and use the *Signal and Ports* dialog to define the signal mapping as covered in *Section 2.3 Sub-Projects* in the TestBencher manual.

Signals can be added manually by using the Add Signal, Add Clock, Add Bus and Add Spacer buttons on the signal button bar. The signal name, HDL type, and direction can be edited using the *Signal Properties* dialog.

| Add Signal |            |

|------------|------------|

| Add Clock  | Add Spacer |

#### To add a Signal, Clock, Bus or Spacer:

- Click the appropriate button in the first group of four. This will add the Signal, Clock, Bus or Spacer to the timing diagram. Spacers are just for adding space to the diagram and do not generate code.

- If you added a signal, clock or bus, then double-click the name of the new object to open the *Signal Properties* dialog.

- Edit the Name. If the signal is to be hooked up to a signal in the HDL model, then use the same name.

- Edit the signal type using the **language Type** drop down list box in the bottom of the dialog.

- Edit the signal size using the MSB and LSB edit boxes. Clocks are always one bit wide.

- Edit the **Direction** using the drop down list box. The following directions are available:

- Output indicates that the signal is output from the diagram.

- **Input** indicates that the signal is what you expect the model under test to generate during simulation (these signals are inputs to the timing transactions, driven by the model under test). In the timing diagram, Sample parameters usually end on an input signal, indicating that the input signal should be checked for an expected value at that point on the signal.

- **Inout** indicates that the signal is bi-directional (see *Section 1.1: Drawing Waveforms and Bi-Directional Signals*). Inout signals contain driven and un-driven signal segments. Driven segments act like signals of type **output**.

- Internal indicates that the signal will only be used internally to the diagram component.

- The **Clock** and **Edge/Level** specify the clocking signal for the waveform. In TestBencher, these will be automatically set by the *Project Wizard* options, however, you can pick a different system clock signal and edge using these controls. TestBencher users can also change the default clock using the *Diagram Properties* clock.

- For Clocks, the clock period, duty cycle, and clock offset can be changed by either clicking on the **Clock Prop**erties button or by Double-clicking on the clock waveform.

The default signal direction and language type for new signals can be set from the *Diagram Settings* dialog (see *Section 3.7: Diagram Settings Dialog - Overview* in the TestBencher manual for more information).

# 1.5 Boolean Equations with Delays

SynaptiCAD's Boolean equations combinatorially relate one signal to other signals in the diagram. To describe a signal with a Boolean equation:

- Double-click on a signal name to open the Signal Properties dialog.

- Make sure the Boolean Equation radio button is selected.

- Enter a Boolean equation into the edit box.

| Boolean Equation: ex. (SIG1 and SIG2) delay 5 |   |

|-----------------------------------------------|---|

|                                               | • |

- To view or edit the Verilog HDL code used by the simulator, select the HDL Code radio button.

The Boolean Equation edit box accepts Boolean equations in VHDL, Verilog, and SynaptiCAD's enhanced equation syntax. The SynaptiCAD format supports the operators: **and**, **or**, **nand**, **nor**, **xor**, **not**, and **delay**. The delay operator takes a signal on the left and a time or parameter name on the right and returns a signal. If a parameter name is used on the right hand side of the delay operator, then the equation will simulate true min/max timing. This true min/max timing analysis is the main advantage that SynaptiCAD's format has over the VHDL or Verilog format. Instead of min/ max timing, Min-Only or Max-Only simulations can be performed by changing the **Options > Simulation Preferences > Timing Model** drop-down list box. Below are sample Boolean equations:

#### (SIG0 and SIG1 and SIG3) delay 20ns

This models a 3-input AND gate with a 20ns delay.

#### (SIG0 delay 20ns) and (SIG1 delay 10ns)

This models an AND gate with 2 different input delays.

#### (SIG0 and SIG1) delay GateDelay

Assume GateDelay is a delay parameter with a min time of 15ns and a max time of 20ns. This models an AND gate with a delay between 15ns and 20ns. Each edge of the simulated signal will have a grey uncertainty region of 5ns.

# **1.6 Advanced Gate Representation**

The **Boolean equation** edit box of the *Signal Properties* dialog can accept several advanced operators, like conditional expressions and signal concatenation. These operators can be used to model multiplexers, tristate gates, and multi-bit signals. The following demonstrates several of these modeling techniques:

**Conditional Expressions for Multiplexers and Tristate gates:** The normal C language conditional expression of *conditional ? if\_expr : else\_expr* can be used inside the Boolean Equation edit box to model multiplexers and tristate gates. Some examples are:

For a Tristate Gate: EnableSig ? SIG0 : 'bz

For a 2-1 MUX: S0 ? SIG0 : SIG1

For a 4-1 MUX: S1 ? (S0 ? SIG0 : SIG1) : (S0 ? SIG3 : SIG2)

**Multi-bit Equations** are specified by setting the **MSB** and **LSB** of the signal (located at the bottom of the *Signal Properties* dialog). To change a simple 1-bit equation to a 4-bit equation, all you have to do is set the MSB of the signals involved to 3.

**Concatenation of Signals** is supported using the Verilog concatenation operator. You must set the **MSB** in the *Signals Properties* dialog to the proper size. If the size of the concatenated signal is larger than the receiving signal, then the most significant bits are dropped. Some examples of the concatenation operator:

- Signal Concatenation: {SIG0, SIG1}

- Concatenating bit-slices: {SIG0[3:0], SIG1[7:4]}

# **1.7 Register and Latch Equations**

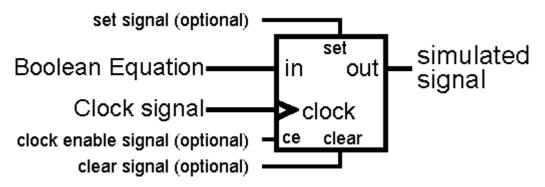

The generation and simulation of registered and latched equations are supported through the Reactive Export and Interactive HDL simulator features. The logic wizard is used to enter information about the circuit for code generation.

#### 12 Chapter 1: Waveforms and Signals

To describe a signal that is registered or latched:

- Double-click on a signal name to open the Signal Properties dialog.

- Make sure the Boolean Equation radio button is selected.

- Enter the input signal name into the **Boolean equation** edit box. The input Boolean equation can either be the name of the input signal or an equation that conditions the input signal.

- Choose the clocking signal from the **Clock** drop-down list box. The clocking signal can be any clock or signal in the timing diagram.

- Choose the type of edge or level triggering from the Edge/Level list box. For a Register circuit choose neg for negative edge triggering, pos for positive edge triggering, or both for edge triggering. For a Latch circuit choose either low or high level latching.

- The Set, Clear, and Clock Enable are optional signals that model the set, clear, and clock enable lines of the

register or latch. If "Not Used" is chosen for a line, then that line is not modeled. These lines can be active

low or high and synchronous or asynchronous depending on the settings in the Advanced Register and Latch

Controls dialog.

- The Advanced Register button opens the Advanced Register and Latch Controls dialog which determine how this individual register is generated. The global defaults can be defined using the Options > Simulation Preferences menu. This dialog controls the following options:

- Clock to Out: Describes the delay from the triggering of the clock signal to a change on the output edge. This setting supports both a Low to High model and a High to Low model.

- Setup: Describes the time for which the input must be stable before the clock-triggering event. If a min/ max time pair is entered, Setup will use the min time. Any violations of this setup time will be reported to the simulation log (see the simulation log information below).

- Hold: Describes the time for which the input must remain stable after the clock-triggering event. If a min/ max time pair is entered, Hold will use the min time. Any violations of this hold time will be reported to the simulation log (see the simulation log information below).

#### **Simulation Log Information:**

Simulation-Enabled products will report timing violations to the **verilog.log** log file, shown in the report window (sample error message shown below). Otherwise, simulation log messages will be reported through the console of the third party simulator that is being used (e.g. ModelSim).

| Advanced Register and Latch Controls                                              |                 |              |          |  |  |

|-----------------------------------------------------------------------------------|-----------------|--------------|----------|--|--|

| Set and Clear<br><u>Set and Clear</u><br><u>Active Low</u><br><u>Asynchronous</u> |                 | 0            | ns<br>ns |  |  |

| Clock Enable                                                                      | Setup:<br>Hold: | 0            | ns<br>ns |  |  |

| OK                                                                                | Cancel          | <u>H</u> elp |          |  |  |

In the Clock Enable area:

- Active Low: If checked, the clock will be enabled when the *clock enable* line is low. If unchecked, the clock will be enabled when the *clock enable* line is high.

In the Set and Clear area:

- Active Low: If checked, the set and clear lines will control the output when they are low. If unchecked, then the set and clear lines will control the output when they are high.

- Asynchronous: If checked, then the set and clear lines will control the output anytime they are active. If unchecked, the model is synchronous and an active set or clear line does not affect the output until the next clock trigger event.

- To view or edit the Verilog HDL code that is used by the simulator, select the HDL Code radio button.

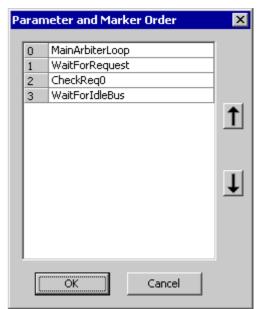

# 1.8 Controlling the Triggering Order of Parameters

Edges on waveforms are responsible for triggering the markers and parameters that are attached to them. If more than one parameter or marker is attached to the same edge then the triggering order can be set using the *Edge Properties* dialog. By default the triggering order is the same as the order in which the objects were attached to the edge. The triggering order is especially important on edges that define the beginning and ending points of a marker loop, because the order determines whether the action occurs inside or outside of the loop.

Note: If a marker is relative to an edge, but not exactly on top of the edge, then order is based off of placement in the timing diagram and will not show up in the order dialog.

#### To order Parameters and Markers attached to the same edge:

- Double-click the edge that triggers the parameters and markers to open the *Edge Properties* dialog.

- Click the **Trigger Order** button to open the *Parameter and Marker Order* dialog.

- Drag and drop the rows to arrange the parameters and markers in the desired order. You can also use the arrow buttons on the right side of the dialog to move selected items up or down.

- If you need to review the properties of an item before setting the order, you can double-click the name of the object in the row to open the *Properties* dialog for that object.

- Click the **OK** button to close the *Parameter and Marker Order* dialog.

- Click the **OK** button to close the *Edge Properties* dialog.

#### Displaying the order of parameter and markers in the timing diagram

It may be useful to display the triggering order for parameters and markers in the timing diagram. This allows the order of execution to be determined at a glance, without opening the *Parameter and Marker Order* dialog. One of the display options for parameters and markers is **Name and Order**. This setting will display the order number for any parameter or marker with an order greater than 1, followed by the name of the parameter or marker. Note that the omission of the number one allows you to make this display setting the global default without displaying an order number when only one parameter or marker is triggered from an edge.

#### To change the Name and Order display for a single marker or parameter:

- Double-click the parameter or marker to open the Parameter Properties or Marker Properties dialog.

- Select the Name and Order option from the Display Label dropdown list.

- Click **OK** to close the dialog and apply the changes.

#### To change the Global Settings for Name and Order:

- Select the **Options > Drawing Preferences (Style Sheet)** menu option. This will open the *Drawing Preferences (Style Sheet)* dialog.

- Select the Name and Order selection from the Parameter Display Label dropdown list.

- Select the Name and Order selection from the Marker Display Label dropdown list.

- Note: These two settings do not need to be the same. You may wish to set only one of these two as the global default.

- Click **OK** to close the dialog and apply the changes.

# 1.9 Sensitive Edges

The edges of signals can be made falling edge sensitive and rising edge sensitive using the check boxes in the *Signal Properties* dialog. Sensitive edges are usually placed on input signals and the code that gets generated causes the transaction to wait for the sensitive edge before continuing.

Sensitive edges cause wait statements to be inserted for that edge. These waits will block the clocking domain that contains the sensitive edge (see *Section 1.10: Transaction Architecture* for more details on clocking domains).

#### To enable sensitive edges on a signal:

- Double-click the name of the signal that you want to watch for events on. This will open the *Signal Properties* dialog.

Note: Sequence Recognition watches the events on single bit signals only.

- Check the **Rising Edge Sensitive** checkbox or the **Falling Edge Sensitive** checkbox. Enabling both checkboxes will cause both rising and falling edges to be sensitive.

- Click the **OK** button to apply the changes and close the Signal Properties dialog.

Sensitive edges will have arrows instead of a line indicating the state transition.

# **1.10 Transaction Architecture**

This section describes how TestBencher models a transaction diagram. A firm understanding of this material will help you avoid errors in your transaction diagrams and speed the process of debugging your system.

TestBencher generates a transaction for each timing diagram in the project. These transactions are *modules* for Verilog, *entity/architecture* pairs for VHDL, *structs* for e, and *classes* for OpenVera, TestBuilder, and SystemC. Regardless of the language, the transactions use the same general architecture. And in all languages, the transactions have a similar functional API that can be used to trigger them (diagram apply calls).

#### **Clock domains**

Inside each transaction there may be one unclocked sequence process and several clocked sequence processes. A sequence process is created for each clock domain in the diagram to drive signals and trigger parameters (Delays, Samples, Holds, Setups, Markers) that are synchronous to the given clock. Each domain will run in parallel (concurrently) once the diagram is started. Typically, there will only be one clock domain in the diagram. But, if you have multiple domains in the diagram, then it's important to know what is placed in each domain if you have looping or blocking parameters. For example, a Marker loop that is attached to the falling edge of CLK will only loop around items that are also in the CLK\_neg clock domain. Items that are in the unclocked domain wouldn't get placed into the loop. Also, items that can potentially block a process (Samples, Markers, Sensitive Edges) will only block the clock domain that they are placed in. The following sections will go into more detail on how blocking and looping constructs work. The table below shows how the clock domain is determined for each type of construct.

| Construct Type           | Clocking Domain                                                  |

|--------------------------|------------------------------------------------------------------|

| Signals                  | Clock and Edge of signal (Signal Properties dialog)              |

| Sensitive Edge           | Clock and Edge of signal that contains sensitive edge            |

| Samples                  | A sample's clock domain is the process that triggers it. See the |

|                          | table below to determine a sample's triggering process.          |

| Delays attached to edge  | If not unclocked, then Clock and Edge in Delay dialog. Other-    |

|                          | wise, the starting edge of the delay sets the clock domain.      |

| Setups                   | Signal and edge that is pointed to by the Setup                  |

| Holds                    | Signal and edge that is pointed to by the Hold                   |

| Markers attached to edge | The relative edge sets the clock domain                          |

| Markers attached to time | Unclocked                                                        |

#### Signals

Signal states are driven based on three factors: how it is drawn, its clocking domain, and the cycle based setting **Include Time Delays** in the *Diagram Settings* dialog. Unclocked signals are driven at the times that the edge transitions are drawn. Clocked signals are driven based on the clocking edges detected during simulation. The **Include Time Delays** option controls whether or not inter-clock cycle delays are generated for clocked signals. If this option is off, then clocked signals are only driven at clock edges (See Section 3.9 Diagram Settings – Language Tabs in the TestBencher manual). The event timing for signals is covered in detail in Section 4.1 Drawing Transactions for TestBencher in the TestBencher manual.

#### Blocking Constructs (Sensitive Edges, Samples, and Markers)

There are three different types of constructs that can be used to block the execution of a clock domain. A *sensitive edge* (*Section 1.9: Sensitive Edges*) will cause its clock domain to wait on the edge, which will block all other items in that same clock domain until the edge is detected. A Sample that has the **blocking** setting checked (*Section 3.3: Interperting Sample Conditions and Blocking Points*) will block its clock domain until the sample completely finishes, including execution of its *then* or *else* action. And a *Wait Until Marker (Section 4.5: Wait Until Marker*) will block its clock domain until the condition specified becomes true. If the marker is attached to an edge it will only check for the condition at each clock edge of the clock domain.

#### Samples

The code for samples will sometimes be generated in a separate process and sometimes within the clock sequence process that triggers it (in-line). Whenever possible, the sample code will be generated in-line to make it easier to debug the generated code. However, if the sample is *non-blocking* and needs to wait for simulation time to pass, then that sample will be placed in its own process or task and triggered by the sequence at the appropriate time. Some examples of samples that need to wait for simulation time to pass are *windowed samples* or samples that are delayed from their triggering point.

The sequence process that triggers the sample is determined from the combination of the triggering edge and the *Samples Properties* dialog *clock* and *edge type* settings.

| Triggering Edge        | Sample Properties              | Triggering Sequence                          |

|------------------------|--------------------------------|----------------------------------------------|

|                        | clock and edge type            |                                              |

| No trigger (time only) | Ignored when no trigger edge   | Unclocked sequence                           |

| Attached to an edge    | Unclocked                      | Trigger edge sequence                        |

| Attached to clock edge |                                | Clock sequence from dialog                   |

| Attached to an edge    | Different than triggering edge | Clock sequence from dialog with a level sen- |

|                        |                                | sitive check on the triggering signal        |

| 58.4n <mark>58.4</mark> r | Ons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50ns       | 100ns      | 150ns  | 200ns | 250r    |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|--------|-------|---------|

| CLK                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |            |        |       | ,       |

| CONTROL                   | and the second s | - <u>-</u> |            |        |       |         |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SAMPLE1    | AC و       | MPLE3  |       |         |

|                           | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Ļ          |            | /IPLEO | ł     | SAMPLE2 |

| DATA                      | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | \$\$expect | edData |       | )       |

The example diagram below contains three domains: CLK pos, CONTROL neg, and Unclocked.

**CLK\_pos:** This is a clocked diagram so most of the graphical elements were automatically created with the clock/edge already set to **CLK** and **pos edge** in the *Properties* dialog of the element.

- SAMPLE2: triggered from the third clock edge.

- SAMPLE0: at second clock edge, a level sensitive check is performed on the CONTROL signal and if it is 0 then the sample will trigger. If instead of a level sensitive check on CONTROL, you want to perform an edge sensitive wait on CONTROL, then set the **falling edge sensitive** check box in *Signal Properties* dialog for the CONTROL signal.

**CONTROL\_neg:** When SAMPLE1 was created we used the *Sample Properties* dialog to change the clock setting to **unclocked**. This setting change will allow SAMPLE1 to be triggered when the CONTROL signal goes negative (compare this to the behavior of SAMPLE0 above).

**Unclocked sequence**: SAMPLE3 is an absolute sample (not attached to an edge) so it will be placed in the unclocked sequence. SAMPLE3 will trigger at 125 ns.

#### **Delay Parameters**

Delays are placed in clock domains based on the same rules that apply to Samples. The only difference is that it is not possible to create a delay that is not attached to an edge. So, Delays will never be triggered by the unclocked sequence.

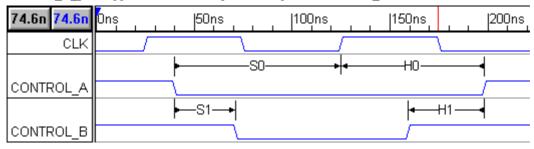

#### **Setups and Holds**

Setups and Holds are placed in clock domains based on the edge that they point to. Since they cannot be attached to time (such as Samples), they will never be triggered by the unclocked sequence.

In the following example there are three different clock domains because the setups and holds point to three different edges:

- CLK\_pos triggers both S0 and H0 at the second positive edge of CLK.

- CONTROL B neg triggers S1 at the first negative edge of CONTROL B.

- CONTROL\_B\_pos triggers H1 at the first positive edge of CONTROL\_B.

### Markers

When looping behavior is needed over a particular set of clock cycles or time, then *Looping Markers* have to be used (see *Section 4.3: Looping markers* for more details on markers). They will only loop over the clocking domain that they are placed in.

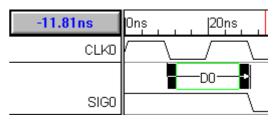

The following example demonstrates how a marker loop might not cover everything in the diagram. The *count* signal has its Clock set to "CLK" and Edge set to "neg". The *SIG0* signal is unclocked. The marker loop will loop over the CLK\_neg clocking domain since the Begin and End loop markers are attached to falling edges of CLK. Since singal *count* is in the same clock domain, during simulation *the signal* will be incremented at each negative clock edge until it reaches 5. Since *SIG0* is Unclocked it is not included in the loop and therefore will only get incremented once.

| 7.0r <mark>9.00</mark> | Ons    | 1        | 100ns |          | 20 <mark>0</mark> ns | 7  300ns | 1 1 | 400     |

|------------------------|--------|----------|-------|----------|----------------------|----------|-----|---------|

|                        |        |          |       | yyhile i | (count < 5)          | Loop End | End | Diagram |

| CLK                    | $\sim$ | <u> </u> |       | ·        | *                    |          |     |         |

| count[3:0]             |        |          | 0     |          | count + 1            |          |     |         |

| SIG0[3:0]              |        | X        | 0     |          | SIGO + 1             |          |     |         |

# **Output Clocks (Clock generators)**

When creating a clocked test bench with Testbencher, there is usually either one timing diagram that has an output clock or the clock is generated in the MUT code. All of the other timing diagrams use an input clock. This makes it easier to synchronize the transactions during simulation.

Each output clock has its own process that generates the clock during a simulation. This clocking process is in addition to any unclocked or clocked processes that are used to synchronize signals and parameters. The clock generation process will take into account as many of the *Clock Properties* as are supported by the generation language.

# **1.11 Diagram Properties**

The cycle based settings and the include file list of a timing diagram are edited using the *TestBencher Diagram Properties* dialog. Diagram properties are significant to the operation of the diagram and can break or dramatically change the way the diagram works during simulation. These properties are saved in the timing diagram file. Other diagram settings that affect the generation of the code but not the operation of the diagram are edited through the *TestBencher Settings* dialog as discussed next in *Section 3.7: Diagram Settings Dialog - Overview* in the TestBencher manual.

To edit the Diagram Properties:

- Open the diagram for which you will be changing the properties.

- In the *Diagram* window, right-click in the signal label area and choose **TestBencher Diagram Properties** from the context menu. This will open the *TestBencher Diagram Properties* dialog.

#### Including HDL Code Library Files

If you have external code modules that you want to make available to the transaction then you can use the interface in the *Diagram Properties* dialog to make that code available. Files can either be included before the transaction, using the equivalent of the Verilog *include* statement, or files can be included inside the module. The method for including code within the transaction varies by language. If possible the code is included using something like the *include* statement and if that concept is not supported then the code is echoed within the transaction. If you have HDL functions or tasks that you would like to write and use within a transaction then use the **Class Methods** dialog as discussed *Section 5.2: Class Methods*. Class Methods is a newer interface that is more flexible and it makes it easier to modify the code and parameters of the functions.

### To Add an HDL Code Library File to the Diagram:

- Click the **Add** button to the right of the appropriate list box to open a file dialog that lets you browse for the include file. Click **Open** to close the file dialog.

Although the code generation for Verilog and VHDL will treat the file lists from this dialog differently, the file selection process for the languages is the same in this dialog.

# **Cycle Based Properties**

The *Cycle Based Properties* control how clocked signals and events are generated. These settings provide default clocking signals and edges to be specified for a diagram. This area also allows existing signals and parameters to be updated to a new clocking signal and edge.

- The **Default Clock** and **Edge** settings provide default values for the clocking signal and sensitive clock edge in a diagram.

- The **Update Existing** button is used to update all signals, samples, delays and anything with a clocking signal defined to the currently selected **Clock** and **Edge/Level**.

| TestBencher Diagram Properties           | ? ×    |

|------------------------------------------|--------|

| Files To Include Before Diagram Module:  |        |

| C:\SynaptiCAD\lib\verilog\tb_clock_max.v | Add    |

|                                          | Delete |

|                                          |        |

| 1                                        |        |

| Files To Include Inside Diagram Module:  |        |

| C:\SynaptiCAD\lib\verilog\sram.v         |        |

|                                          | Add    |

|                                          | Delete |

|                                          |        |

| Cycle Based Properties                   |        |

| Default Clock: clk   Edge:               | pos 💌  |

| Update Existing                          |        |

| OK <u>C</u> ancel                        |        |

# **Chapter 2: Delays, Setups and Holds**

Timing diagrams can include graphical parameters like delays, setups, holds, and samples. These parameters generate transaction code that monitors and conditionally controls signal transitions. By combining and chaining together the parameters, you are graphically describing temporal expressions that will execute during simulation. In TestBencher, Temporal Expressions can also be entered manually using a signal as described in *Section 4.6: Temporal Expressions for TestBencher* in the TestBencher Manual.

This chapter will cover delays, setups, and holds that are parameters that perform actions between two signal transitions. Samples are placed on signal states (not transitions) and monitor the state of a signal. Samples are the main type of parameter used in TestBencher timing diagrams and they are covered in detail in *Chapter 3: Transaction Samples*.

#### Delays

Delays are used to specify a fixed time between signal transitions. The time between signal transitions can be a hard coded value or it can be a variable that is set during simulation. Delays can conditionally drive state values by triggering from a sample or by using an internal delay condition. The condition is checked after the delay is triggered, and before the delay time has been waited for. This is especially good for modeling control signals that go active after certain conditions in the transaction are met.

#### **Setups and Holds**

Setups and Holds perform a check to determine if a signal is stable with respect to another signal. The graphical setup and hold parameters perform a one-time check between two signal transitions. A continuous check between two signals can also be created by using the properties for the signal.

# 2.1 Adding and Editing Parameters

Parameters are added by selecting a parameter button on the button bar, left clicking on the relative edge, and then right clicking on the second edge in the waveform window. After a parameter is added, its values can be edited by doubleclicking on the parameter to open the *Parameter Properties* dialog. The properties for each parameter type are discussed in the section for that type.

To add a Delay, Setup, or Hold:

- Select the parameter button on the Signal Button Bar for the type of parameter you want to add.

| Add Signal | Add Bus    | Delay | Setup | Sample | HIGH | เก๋พ   | TBL | VAL | INVal | WHI | win | HEX |

|------------|------------|-------|-------|--------|------|--------|-----|-----|-------|-----|-----|-----|

| Add Clock  | Add Spacer | Hold  | Text  | Marker | 1    | $\sim$ |     | μ   |       | 2:0 | ~   | -   |

- Click on a transition to select it. For a delay this is the forcing transition. For a setup or hold this is the transition that will be monitored.

- Right-click on the second transition to add a parameter between the first and second transitions. For a delay this is the transition that will be moved. For a setup or hold this is the control signal.

- Double-click the name of the parameter to open the *Parameter Properties* dialog for that parameter and edit the properties of the parameter.

The *Parameter Properties* dialog has many settings that control how the parameter is displayed in the timing diagram and these features are covered in the Timing Diagram Editor on-line help *Section 4.4: Parameter Properties* in the TestBencher manual. TestBencher uses only a few controls for code generation and these are discussed below. A few additional controls are available for delays (discussed in *Section 2.2: Delays*) and samples (discussed in *Chapter 3: Transaction Samples*). The following controls are common to all parameters and are used in code generation:

- The Name edit box allows the user to specify the name of the parameter.

- The **Min** and **Max** edit boxes specify the minimum and maximum time for the parameter to execute. Each type of parameter handles the **Min** and **Max** values differently; for more information, see the sections on delays (*Section 2.2*), setups and holds (*Section 2.4*), and samples (*Chapter 3*).

- The Is Apply Subroutine Input checkbox, for TestBencher, allows you to generate ports between the Component Model and the timing transaction with which to specify the values to use for the Min and Max settings of the parameter. If only one of the values is specified, then a port will only be made for that value. If there is no value specified for either setting, then a port will be made for the min value by default.

- The Enable HDL Code Generation checkbox allows you to turn the code generation for the parameter on and off without removing the parameter from the timing diagram. This checkbox must be checked in order to produce any HDL code for the parameter.

- Note: The HDL code generation for all delays, samples, and markers in a timing diagram can be disabled through the *TestBencher Diagram Settings* dialog. See *Section 3.8: Diagram Settings Dialog - Overview* in

| ietup Prop                                                             | erties 📃 🔀                             |  |  |  |  |  |

|------------------------------------------------------------------------|----------------------------------------|--|--|--|--|--|

| Name:                                                                  | \$0                                    |  |  |  |  |  |

| Min:                                                                   |                                        |  |  |  |  |  |

| Max:                                                                   |                                        |  |  |  |  |  |

| Comment:                                                               |                                        |  |  |  |  |  |

| Hide Bow Change all instances Dutward Arrows Is Apply Subroutine Input |                                        |  |  |  |  |  |

|                                                                        | from SIG0(24.576) to SIG1(59.392)      |  |  |  |  |  |

| Display L                                                              | abel: Global Default                   |  |  |  |  |  |

| Custom:                                                                | %n v=%mv,%Mv f=%mf,%Mf m=%mm,          |  |  |  |  |  |

| 🔲 Hi <u>d</u> e                                                        | User Placed                            |  |  |  |  |  |

| Enable HDL Code Generation                                             |                                        |  |  |  |  |  |

| HDL <u>C</u> or<br>OK                                                  | de Library Prev Next Cancel Apply Help |  |  |  |  |  |

the TestBencher manual for more information on this feature.

# 2.2 Delays

A delay specifies a fixed time between two signal transitions. Delays can also conditionally drive their second edge. In TestBencher, the value for the delay time can be passed into the delay at simulation so that delays can be used to perform sweep tests to see when a circuit will fail.

The first edge (left most edge) that the delay is attached to is called the trigger edge. If the trigger edge is on a clocked signal then the delay will activate at the next clock edge if a level sensitive check of the trigger signal passes. If the trigger edge for the delay is on an unclocked signal, then the delay will activate when the signal transition occurs. If the level sensitive check fails, or if the unclocked trigger signal never transitions then the delay will not activate.

Once a delay is activated, then the delay process will wait for the amount of time (or clock cycles) specified in the min or max value of the parameter, and then drive the second edge. For more information, see *Section 1.10 Transaction Architecture*.

#### To add a Delay to a Timing Diagram:

- Click the Delay button on the Signal Button Bar.

- Click on a transition to select it. This transition is the forcing transition.

- Right-click on the second transition to add a delay between the first and second transitions. This transition is the transition that will be delayed.

- Double-click on the delay to open the *Delay Properties* dialog. Most of the controls in the *Delay Properties* dialog were covered in *Section 2.1 Adding and Editing Parameters*.

The following controls are specific to delays:

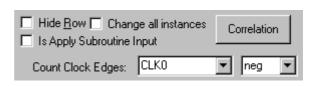

- Count Clock Edges determines if the Min and Max settings are time or cycle based values. If the delay is *Unclocked* then the values are time. If a clock is specified then the values are numbers of clock cycles.

- Min and Max set the minimum and maximum

time or number of clock cycles to be used for the delay. At simulation time only one value min, max, or typical (average of min & max) will be used. In TestBencher, the *Diagram Settings* dialog (discussed in *Section 3.7: Diagram Settings Overview* in the TestBencher manual), has the settings that determine which value will be used during simulation. If only one of the two settings has been given a value (min or max), the other setting will internally be given the same value.

- HDL code button opens the *Boolean Condition* for Delay dialog, that stores the condition that is checked before the delay drives the second edge. By default the condition is TRUE. You can type in the text for a new condition in the generated language. The condition can be any equation that evaluates to a TRUE or FALSE at simulation time. If the condition is not true after the triggering

| Boolean Condition For Delay | ? × |

|-----------------------------|-----|

| Conditional Test: TRUE      |     |

| OK Cancel                   |     |

edge is detected, then the second edge will not be driven. The condition must be written in the generated language of the transaction. Note: If the condition is based on state values that occur during simulation, a graphical conditional delay can be constructed by triggering the delay from a sample parameter (see *Section 3.4: Samples Triggering a Delayed Transition or Another Delay*).

# 2.3 Resolving Multiple Delays

If the same edge is affected by multiple delays, there will be several possible ways for TestBencher to resolve the actual delay. The value for the edge is calculated based on the **Multiple Delay Resolution** setting in the *Edge Properties* dialog. The default setting for the timing diagram is set in the **Options > Design Preferences** dialog.

To open the Edge Properties dialog:

- Double-click on the edge to open the *Edge Properties* dialog.

- In the Multiple Delay Resolution section, choose one of *Transition Settings*:

- Earliest Transitions uses the delay that will place the edge as early in the diagram as possible.

- Latest Transitions uses the delay that will place the edge as late in the diagram as possible.

- Max Uncertainty and Min Uncertainty are not currently supported for TestBencher Code generation.

| Edge Properties                                                                           | ? ×                                                                                                                                                 |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Edge Placement<br>Min: 30<br>Max: 30<br>Min Uncertainty: 0<br>Uncertainty =0 ns<br>Locked | Multiple Delay Resolution<br>© Default<br>© Earliest Transitions<br>© Latest Transitions<br>© Max Uncertainty<br>© Min Uncertainty<br>Trigger Order |

| OK Cancel                                                                                 | Driven (for inout signals only) <u>Apply</u> <u>Prev</u> <u>Next</u>                                                                                |

# 2.4 Setups and Holds

Setups and Holds check timing requirements for a design. **Setups** are the minimum time necessary for a signal to be stable before a control signal transition. **Holds** are the minimum time that a signal must be stable after a control signal transition. Setups and Holds perform one check between two signal transitions. If the setup or hold fails then it outputs a warning in the simulation log file and prints the expected and actual values. If you want to perform a continuous check between two signals you can use the method described in *Section 5.5 Creating Continuous Setups and Holds* in the TestBencher manual.

To create a setup or hold:

- Click the Setup or Hold button.

- Click on a transition to select it. This is the transition that will be monitored.

- Right-click on a second transition to add a setup or hold between the first and second transitions. This is the control signal.

- Double-click on the setup or hold to open the *Parameter Properties* dialog. Most of the controls in the *Parameter Properties* dialog were covered in *Section 2.1 Adding and Editing Parameters*.

The following controls are specific to setups and holds:

- The **Min** field sets the minimum time that the data transition can occur before a setup or after a hold on the control signal.

- The **Max** field sets the maximum time that the data transition can occur before or after the control transition. This field is optional and usually not specified for setups and holds.

If a time is specified for the Max field, then the data transition must occur between the Min and Max times.

- The **Outward Arrows** checkbox changes the direction that the arrows on the parameter are drawn. This does not affect code generation but it is a popular graphical feature.

# **Chapter 3: Samples**

Samples generate the self-testing code within a transaction using either temporal expressions or procedural code that produces the same functionality as a complex temporal expression. In TestBencher, temporal expressions can also be entered manually as described in *Section 4.6: Temporal Expressions for TestBencher* in the TestBencher manual. Samples are used to monitor the signal values coming back from the model under test. Samples can be run at a specific time, triggered from an event, or triggered from another sample. The value that is sampled can be exported to the top-level module. This could be used, for instance, to provide an input value for a state variable in another timing transaction or to determine if a specific timing transaction is to be executed or not. Samples can also be used to trigger a delay based on its success or failure. Below are the terms used to describe the different monitoring times and triggering events of a sample.

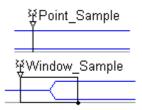

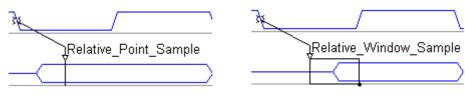

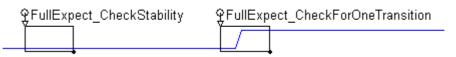

# **Monitoring Time**

Samples that monitor a signal at a specific time are called *Point Samples*. And samples that monitor a signal over an interval of time are called *Window Samples*. Window samples are useful for testing that the value of a given signal does not change over a specified time frame, or for verifying that the signal goes through a specified sequence of states. Window samples draw themselves with a box indicating the monitoring interval. If you need to sample over a large window and you do not want to display it graphically then you can use the *Multiplier* control in the *Code Generation Options* dialog described in *Section 3.2 Sample Condition and Actions*.

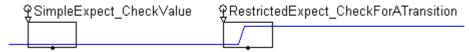

# **Triggering Process**