# SynaptiCAD Tutorials

www.syncad.com

#### SynaptiCAD Tutorials (rev 10.0) copyright 1994-2005 SynaptiCAD

Trademarks

- Timing Diagrammer Pro, WaveFormer Pro, TestBencher Pro, VeriLogger Pro, DataSheet Pro, BugHunter Pro and SynaptiCAD are trademarks of SynaptiCAD Inc.

- VERA, OpenVera, VCS, and VCSi are trademarks of Sysnopsys, Inc.

- NC Verilog, NC VHDL, and Verilog-XL are trademarks of Cadence Design Systems, Inc.

- Pod-A-Lyzer is a trademark of Boulder Creek Engineering.

- PeakVHDL and PeakFPGA are trademarks of Accolade Design Automation Inc.

- V-System and ModelSim are trademarks of Model Technology Incorporated.

- Viewlogic, Workview, and Viewsim are registered trademarks of Viewlogic Inc.

- HP and Agilent are trademarks of Hewlett Packard.

- Tektronix copyright Tektronix, Inc.

- PI-2005 and PI-Pat are trademarks of Pulse Instruments.

- Timing Designer and Chronology are registered trademarks of Chronology Corp.

- DesignWorks is a trademark of Capilano Computing.

- Mentor and QuickSim II are registered trademarks of Mentor Graphics Inc.

- OrCAD is a registered trademark of OrCAD.

- PSpice is a registered trademark of MicroSim.

- Windows, Windows NT, and Windows 95/98/2000 are registered trademarks of Microsoft.

All other brand and product names are the trademarks of their respective holders.

Information in this documentation is subject to change without notice and does not represent a commitment on the part of SynaptiCAD. Not all functions listed in manual apply to Timing Diagrammer Pro, WaveFormer Pro, DataSheet Pro, or VeriLogger Pro. The software and associated documentation is provided under a license agreement and is the property of SynaptiCAD. Copying the software in violation of Federal Copyright Law is a criminal offense. Violators will be prosecuted to the full extent of the law.

No part of this document may be reproduced or transmitted in any manner or by any means, electronic or mechanical, including photocopying and recording, for any purpose without the written permission of SynaptiCAD.

For latest product information and updates contact SynaptiCAD at:

web site: http://www.syncad.com email: sales@syncad.com phone: (540)953-3390

# **Table of Contents**

| Table of Contents                                  |   |

|----------------------------------------------------|---|

| Introduction                                       | 6 |

| Basic Drawing And Timing Analysis                  |   |

| 1) Set the Base Time Unit                          |   |

| 2) Set the Display Time Unit                       |   |

| 3) Add the Clock                                   |   |

| 4) Add Signals                                     |   |

| 5) Drawing Signal Waveforms                        |   |

| 6) Edit Signal Waveforms                           |   |

| 7) Adjust Diagram to Match Figure                  |   |

| 8) Moving and Reordering Signals                   |   |

| 9) The Right Mouse Button                          |   |

| 10) Add the D Flip-Flop Propagation Delay          |   |

| 11) Add the Inverter Propagation Delay             |   |

| 12) Add the Setup for the Dinput to Clock          |   |

| 13) Add a Free Parameter                           |   |

| 14) Using Formulas and Constants                   |   |

| 15) Summary                                        |   |

| Interactive HDL Simulation Tutorial                |   |

| 1) Interactive HDL Simulation                      |   |

| 2) Generate Waveforms From Boolean Equations       |   |

| 3) Boolean Equations with Delays                   |   |

| 4) Register and Latch Signals                      |   |

| 5) Set and Clear Lines                             |   |

| 6) Multi-bit Equations                             |   |

| 7) Experiment with Behavioral HDL Code             |   |

| 8) Summary                                         |   |

| Waveform Generation And Bus Tutorial               |   |

| 1) Generate Waveforms from Temporal Equations      |   |

| 2) Bus Overview                                    |   |

| 2.1) Creating Virtual Buses                        |   |

| 2.2) Creating Group Buses                          |   |

| 2.3) Creating Simulated Buses                      |   |

| 3) Summary                                         |   |

| Display and Documentation Tutorial                 |   |

| 1) Controlling the Parameter Display String        |   |

| 2) Repeating Parameters                            |   |

| 3) Editing Waveform Edges From an Equation         |   |

| 4) Drag and Drop Parameter End Points              |   |

| 5) Adjusting the Vertical Placement of a Parameter |   |

| 6) Clock Jitter and Display                        |   |

| 7) Markers                                         |   |

| 8) Edit Text Blocks                                |   |

| 9) Summary                                         |   |

| Advanced Modeling and Simulation                   |   |

| 1) Set up a New Timing Diagram                                      |    |

|---------------------------------------------------------------------|----|

| 2) Generate the Clock, Draw Waveforms, and Use Waveform Equations   |    |

| 3) Modeling State Machines                                          |    |

| 4) Checking for Simulation Errors                                   |    |

| 5) Incremental Simulation                                           |    |

| 6) Modeling Combinatorial Logic                                     |    |

| 7) Entering Direct HDL Code for Simulated Signals                   |    |

| 8) Modeling n-bit Gates                                             |    |

| 9) Incorporating Pre-Written HDL Models into Waveformer Simulations |    |

| 10) Modeling the Incrementor and Latch Circuit                      |    |

| 11) Modeling Tri-State Gates                                        |    |

| 12) Debugging External Verilog Models                               |    |

| 13) Verify the Histogram Circuit                                    |    |

| 14) Controlling the Length of the Simulation                        |    |

| 15) Editing Verilog Source Files                                    |    |

| 16) Simulating Your Model with Traditional Verilog Simulators       |    |

| 17) Summary                                                         |    |

| Parameter Libraries                                                 | 59 |

| 1) Adding Libraries to the Project's "Library Search List"          | 59 |

| 2) Setting Library Specifications                                   |    |

| 3) Startup Library Configuration                                    |    |

| 4) Referencing Parameters in Libraries                              |    |

| 5) Using Macros to Examine Tradeoffs Between Different Libraries    |    |

| Advanced HDL Stimulus Generation                                    |    |

| 1) Getting Started                                                  |    |

| 2) Default Mappings: Hex and Binary Translations                    |    |

| 3) Generating Verilog Code                                          |    |

| 4) VHDL - Advanced Data Types                                       |    |

| 5) Exporting to VHDL                                                |    |

|                                                                     |    |

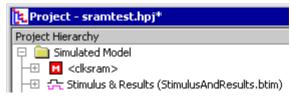

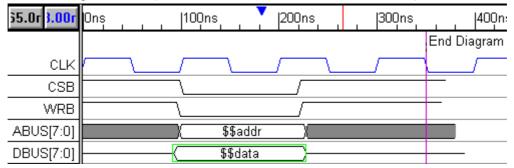

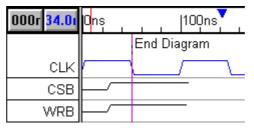

| Basic Verilog Simulation                                            |    |

| Part 1: Project Management and Simulation                           |    |

| 1.1) Add Files to the Project                                       |    |

| 1.2) Build the Tree and Use the Editor Window                       |    |

| 1.3) Simulate the Project                                           |    |

| 1.4) Watch and View Internal Signals                                |    |

| 1.5) Save the Project, Waveforms and Source Code                    |    |

| Part 2: Graphical Test Bench Generation                             |    |

| 2.1) Remove TestBench Model and Clean Results Diagram               |    |

| 2.2) Build the Project and Examine the Black Signals                |    |

| 2.3) Use the Debug Run and Simulation Mode                          |    |

| 2.4) How to Draw Waveforms                                          |    |

| 2.5) How to Edit Waveforms                                          |    |

| 2.6) Draw the Stimulus Waveforms                                    |    |

| 2.7) Simulate Using the Auto Run Simulation Mode                    |    |

| 2.8) Import and Generate Waveforms                                  |    |

| 3) Breakpoints, Stepping and Tracing                                |    |

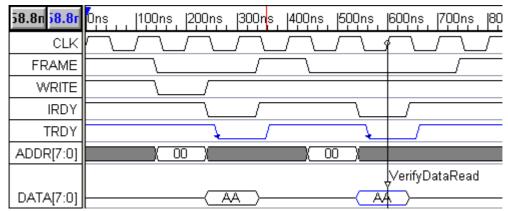

| Reactive TestBench Tutorial                                         |    |

| 1) Overview                                                         | 77 |

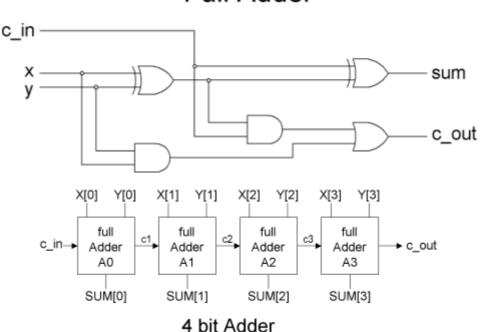

| 2) The Model Under Test                                             | 77 |

|                                                                     |    |

|   | 3) Create Signals                                       | . 78 |

|---|---------------------------------------------------------|------|

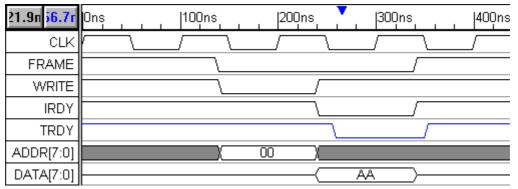

|   | 4) Draw Single Write (without waiting on TRDY)          | . 79 |

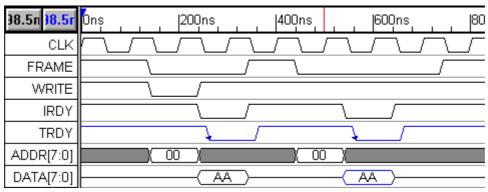

|   | 5) Add Wait for TRD Assertion                           |      |

|   | 6) Draw Single Read                                     |      |

|   | 7) Add a Sample to Verify Data Read from MUT            |      |

|   | 8) Drive Data Using a Test Vector Spreadsheet File      |      |

|   | 9) Create For-Loop to Perform Multiple Writes and Reads |      |

|   | 10) TestBencher Pro Transactor - Add Address Argument   |      |

|   | 11) Alternatives                                        |      |

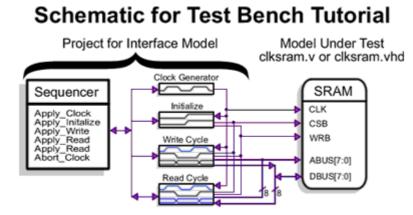

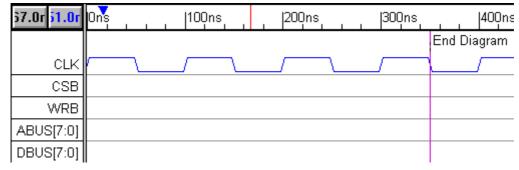

| Т | estBencher Pro: Basic Tutorial                          |      |

|   | 1) Create a Project                                     | . 85 |

|   | 2) Create the Write Cycle Transaction Diagram           |      |

|   | 3) Create the Read Cycle Transaction Diagram            | . 88 |

|   | 4) Create the Initialize Transaction Diagram            |      |

|   | 5) Modify the Sequencer Process                         | . 91 |

|   | / / 1                                                   |      |

|   | 6) Generate Test Bench and Simulate                     | . 94 |

# Introduction

There are several tutorials shipped with all versions SynaptiCAD's software. These tutorials demonstrate everything from how to draw basic timing diagrams to advanced VHDL and Verilog simulation techniques. The following chart describes the recommended tutorials for each of our products.

|                                   | Timing<br>Diagrammer | WaveFormer | DataSheet | TestBencher | VeriLogger<br>BugHunter |

|-----------------------------------|----------------------|------------|-----------|-------------|-------------------------|

| Basic Drawing and Timing Analysis | ****                 | ****       | ****      | ***         |                         |

| Interactive HDL Simulation        |                      | ****       | *         | *           |                         |

| Waveform Generation and Bus       | ****                 | ****       | ***       | *           | *                       |

| Display and Documentation         | ****                 | **         | ****      | **          |                         |

| Advanced Modeling and Simulation  |                      | ***        | *         | *           |                         |

| Parameter Libraries               | **                   | **         | **        |             |                         |

| Advanced HDL Stimulus Generation  |                      | ***        |           |             |                         |

| TestBencher Pro: Basic Tutorial   |                      |            |           | ****        |                         |

| Basic Verilog Simulation          |                      |            |           |             | ****                    |

#### Table 1: Determining which tutorials to perform

After installing one of SynaptiCAD's products, choose the **Help** > **Tutorials** menu to open the tutorial help page. Each tutorial can be printed by using the print command in the help window.

**Evaluators:** If you are evaluating the product we recommend that you do at least the General Design tutorials. These will give you a good idea of the flexibility of the product. If you design in VHDL or Verilog you should also look at the HDL tutorial and the TestBencher tutorial.

#### **General Design Tutorials**

- The **Basic Drawing And Timing Analysis** tutorial explains the basic timing diagram editing environment: how to set the base time unit and the display time unit of a timing diagram; how to draw and edit signals, delays, and setups; and how to perform time measurements. This tutorial is essential to anyone evaluating or learning to use any SynaptiCAD product.

- The **Interactive HDL Simulation** tutorial explores the various time saving techniques of generating waveforms using equations. This tutorial explains how the Interactive HDL Simulator can simulate Boolean Equations with delays, register and latched signals, and behavioral Verilog code. It also demonstrates how instant resimulations can be performed when input waveforms are modified, so that tedious calculations, once done by hand, are now automatically generated.

- The **Waveform Generation and Bus** tutorial demonstrates techniques for working with multiple bit signals. These techniques include generating the waveforms and automatically labeling those waveforms using equations. This tutorial also covers how to create Virtual, Group, and Simulated buses for solving different design problems. These features augment the drawing environment and provide a quick way to generate signals without having to draw each signal transition.

- The **Display and Documentation** tutorial demonstrates different methods for controlling the information that is displayed by delays, setups, holds, and samples. It also describes how to manipulate the vertical placement of a parameter, and how to change the transition attachments. These features allow you to control the information displayed and the appearance of the timing diagram.

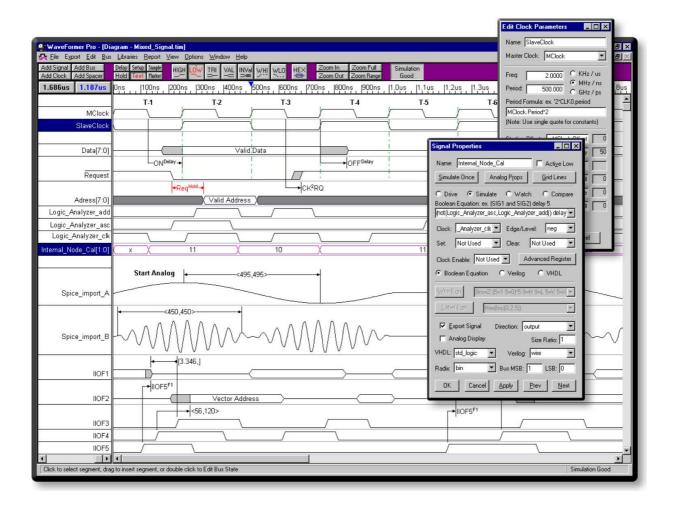

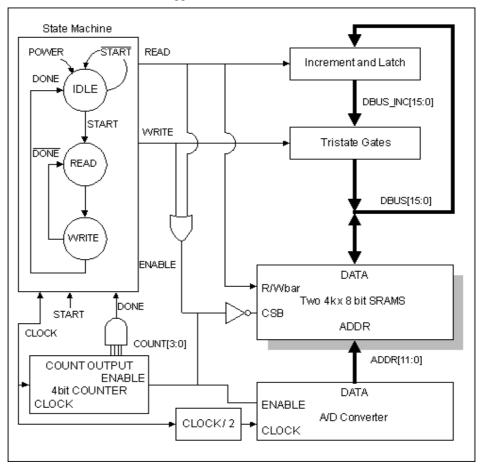

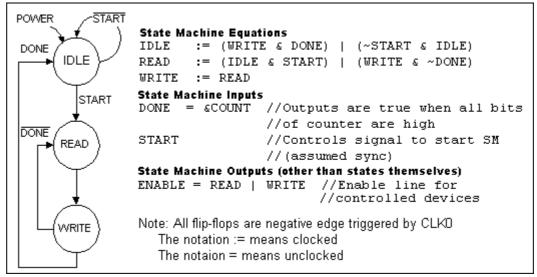

- The **Advanced Modeling and Simulation** demonstrates how WaveFormer Pro can quickly model and simulate a digital system of moderate complexity. This tutorial will teach you how to model state machines using Boolean equations, use the Report window to find simulation errors, enter direct HDL code, model tristate gates, model n-bit gates, and call external HDL models. All WaveFormer and TestBencher Pro users should do this tutorial.

#### **Specialized Feature Tutorials**

- The **Parameter Libraries** tutorial covers the use of libraries and macro lists. This tutorial is important to do before starting a large project. Using Libraries and macro lists can save you a great deal of time if they are configured properly.

- The Advanced HDL Stimulus Generation tutorial covers the basic concepts of HDL stimulus generation, such as graphical waveform states, language-independent hexadecimal and binary bus translation, and user-de-fined types. WaveFormer Pro and TestBencher Pro users should do this tutorial.

- The **Basic Verilog Simulation** tutorial covers the basic simulation features of BugHunter Pro. This tutorial also discusses how to create and manage projects, as well as how to build and simulate your design. BugHunter Pro and TestBencher Pro users should perform this tutorial.

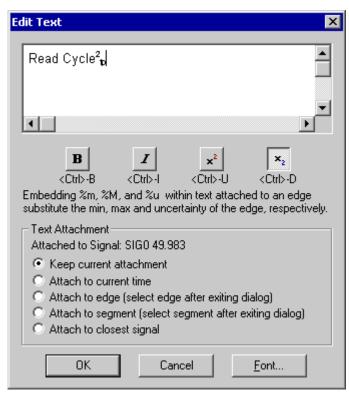

- The **TestBencher Pro: Basic TestBencher Tutorial** covers the basic concepts of using TestBencher Pro to generate bus-functional models for Verilog, VHDL, & OpenVera. It covers signal properties (type, direction, vector size, and bi-directional segments), samples, parameterized state values, end diagram markers, interface diagrams, modifying top-level template files, and generating test benches. TestBencher Pro users should do this tutorial.

# **Basic Drawing And Timing Analysis**

This tutorial demonstrates the basic timing diagram editor features. It teaches you how to draw timing diagrams using delays, setups, clocks and part libraries and how to use timing diagrams to help detect timing errors in digital designs. It also covers the waveform editing features, measurement and quick access buttons.

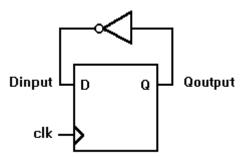

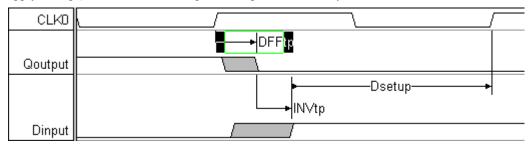

You will draw the timing diagram for the circuit shown in Figure 1. This circuit divides the clock frequency in half. Both the flip-flop and the inverter have propagation times that delay the arrival of the Dinput signal. If the Dinput is delayed too long it will violate the data-to-clock setup time. This increases the risk of the flip-flop failing to clock in the data and may lead to the flip-flop entering a metastable state.

Figure 1: Tutorial circuit

#### **Circuit Parameters:**

| clk    | 20MHz        | (50ns period)                                            |

|--------|--------------|----------------------------------------------------------|

| DFFtp  | 5-18ns       | D flip-flop (74ALS74): Clock to Q propagation time       |

| Dsetup | 15ns minimum | D flip-flop (74ALS74): D to rising edge Clock setup time |

| INVtp  | 3-11ns       | Inverter (74ALS04): propagation time                     |

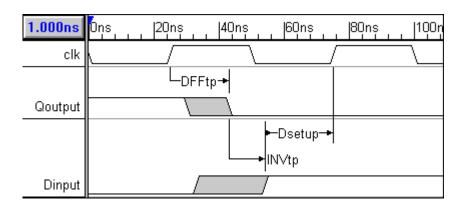

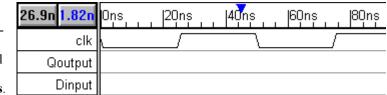

Figure 2 is the completed timing diagram. The first thing you may notice is the gray signal transitions caused by the min/max values of the component delays. The gray areas of the signal transitions are uncertainty regions, which indicate that the signal may transition any time during that period. This is a little disconcerting especially if you have been using a low-end simulator that cannot compute both min and max at the same time. This representation shows the entire range of possible circuit performance. With WaveFormer Pro, there won't be any surprises during production when you get components at extreme ends of their tolerance range.

Figure 2: Completed Timing Diagram

# 1) Set the Base Time Unit

At the beginning of each project, you will set the base time unit. The base time unit is the smallest representable amount of time that WaveFormer Pro can display. The base time unit determines the range of times that can be represented in your timing diagram. All time values are internally stored in terms of the base time unit.

In the circuit in Fig.1, the propagation times for the gates are in units of nanoseconds and the clock has a period of 20ns. Generally it is a good idea to set the base time unit for your project one unit below the units you are working in for best rounding performance during division operations (clock frequencies are inverted and stored internally as clock periods). Therefore we will set the base time units to picoseconds. To set the base time unit:

> 1.Select the **Options > Base Time Unit** menu option. This displays the *Base Time Unit* dialog box with radio buttons that set the base time unit. The other options con-

| Base Time Unit Settings 🛛 🛛 🔋 🗙                                                                |

|------------------------------------------------------------------------------------------------|

| Base Time Unit           Image: New Diagrams Settings         Image: O Active Diagram Settings |

| Base Time Unit Settings                                                                        |

| Default Settings                                                                               |

| Base Time Unit                                                                                 |

| Cfs ●ps Cns Cµs Cms                                                                            |

| How to Change Units                                                                            |

| Keep All Times (5ns -> 5000ps)                                                                 |

| Scale All Times (5ns -> 5ps)                                                                   |

| C Scale Parm Times, Keep Signal Times                                                          |

| OK Cancel                                                                                      |

trol how any existing parameters or signals are changed when the base time unit is changed and have no effect on an empty timing diagram. See the on-line help if you want to know more about these options.

- Click on the **ps** radio button to make picoseconds the base time unit (if it is not already selected).

- 3. Press the **OK** button to close the dialog.

#### 2) Set the Display Time Unit

Next you need to set the display time unit. The display time unit sets the units for times which you enter and for times which are displayed. Set the display time unit to the units you most commonly use in the design. To set the display time unit:

- Select the Options > Display Unit menu option. This will display a submenu of display time units. The checked time is the current display time unit (Default is ns = nanoseconds).

- 2. Click on **ns**, to make nanoseconds the display time unit if it is not already checked.

| Options Window Help   |       |

|-----------------------|-------|

| Display Unit [ns] 🔹 🕨 | 1fs   |

| Base Time Unit [ps]   | 1ps   |

| Read-Only Mode        | 🖌 1ns |

| Rich Text Support     | 1µs   |

| Grid Settings         | 1ms   |

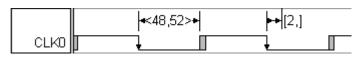

## 3) Add the Clock

First we will create the clock. The clock is named **clk**, has a period of **50**ns (20MHz), and starts with a low segment.

#### To add a clock:

- 1. Move the mouse cursor over the Add Clock button Add Clock (DO NOT CLICK), located in the top left hand corner of the Diagram Window.

- 2. Notice that the status bar at the very bottom of the window reads "Left click to add a clock signal, right click to set clock name prefix" This status bar changes depending on the mouse location and the mode that you are in. Move the mouse around and watch the status bar change. The status bar is very useful when you want to know what buttons do or when you need to know what to do next in the middle of a program operation.

Left click to add a clock signal, right click to set clock name

- 3. Click the Add Clock button.

- 4. The Edit Clock Parameters dialog box will appear.

- 5. Enter the name **clk** in the *Name*: edit box.

- 6. Enter **50** in the *Period:* box. Make sure the **MHz/ns** radio button is selected. Note that the frequency will change to match the new period value, when you move the selection to another control.

- 7. Check the **invert** check box. Clocks are normally displayed high at time zero, so "invert" makes the clock start low at time zero.

- 8. Click the **OK** button to close the dialog box.

**Note:** For more information on clocks, master clocks, clocks with formulas, and clock grids read *Chapter 2: Clocks* in the on-line help. If you made a mistake designing the clock, then double left click on the clock segment to reopen the *Edit Clock Parameters* dialog box. Double left clicking on a clock edge opens up the *Edge Properties* dialog box which displays the edge time. You may also reach the *Edit Clock Parameters* dialog box by double clicking on the clock name and choosing the clock properties button in the *Signal Properties* dialog.

# 4) Add Signals

Next, add two signals and name them "Qoutput" and "Dinput".

1. Click twice on the Add Signal button

Add Signal to add two signals. The signals will have default names such as SIG0 and SIG1.

2. **Double left click** on the **SIG0** signal name to open the *Signal Properties* dialog.

| dit Clock Parameters                            |       | ? ×                              |

|-------------------------------------------------|-------|----------------------------------|

| Name: clk                                       |       |                                  |

| Reference Clk: None                             |       | •                                |

| Freq:         20.           Period:         50. |       | (Hz / us<br>/Hz / ns<br>iHz / ps |

| Period Formula: ex. 2*CLK0.perio                | bd    |                                  |

| 150                                             |       |                                  |

| Starting Offset:                                | 0     | 0                                |

| Duty Cycle %:                                   | 50    | 50                               |

| Rise Jitter (range):                            | 0     | 0                                |

| Fall Jitter (range):                            | 0     | 0                                |

| Min L to H:                                     | 0     | 0                                |

| Max L to H:                                     | 0     | 0                                |

| Min H to L:                                     | 0     | 0                                |

| Max H to L:                                     | 0     | 0                                |

| Rising Delay Correlation:                       | 100   | %                                |

| Falling Delay Correlation:                      | 100   | %                                |

| Rise to Fall Correlation:                       | 100   | %                                |

| Invert (Starts Low)                             |       |                                  |

| ок с                                            | ancel |                                  |

3. Enter **Qoutput** into the **Name:** edit box. (DO NOT CLOSE THE DIALOG)

| Signal Pr | operties | ? ×        |

|-----------|----------|------------|

| Name:     | Qoutput  | Active Low |

- 4. Click the **Next** button or **ALT-N** to move to the next signal on the list. SIG1 is now displayed in the *Name:* edit box.

- 5. Enter **Dinput** into the **Name:** edit box and press the **OK** button to close the dialog.

If you accidentally close the *Signal Properties* dialog, double click on the signal name to open the dialog again. The Boolean Equation and Simulation features of the *Signal Properties* dialog are covered in *the Interactive HDL Simulation* tutorial. The *Signal Properties* dialog is modeless, so you can leave the dialog open while you perform actions on the timing diagram.

## 5) Drawing Signal Waveforms

Next, we will draw some random waveforms to become familiar with the drawing environment.

Notice the buttons with the waveforms drawn on them. These are the State Buttons. The active button is colored red and indicates the type of signal state that will be drawn next. In this case, the HIGH signal state is active.

2. Move the mouse

cursor to inside the *Diagram* window at the same level as the signal name **Qoutput**, and at about **40ns**.

3. Click to draw a

waveform segment from 0ns to the cursor. Notice that a HIGH signal was created.

4. A different state button is now activated. The State Buttons automatically toggle between the two most recently activated states. The small red T above the signal name denotes the toggle state, for instance. (If you have a 3 button mouse, click the middle mouse button to toggle between the two most recently activated state buttons.)

- 5. Move the cursor to about **80ns** on the same signal and **left click**. Now a LOW segment is drawn from the end of the HIGH signal to the location of the cursor.

- 6. Left click on the TRI button to activate the tristate State Button and draw another waveform segment.

7. Draw more segments, using all the states except the HEX button. The HEX state button is used in defining multi-bit signals and signals which have a user defined VHDL type. This button is covered in later tutorials. For now, experiment with the graphical states.

Your drawing should be a mess, or at least look nothing like Figure 2.

# 6) Edit Signal Waveforms

There are four main editing techniques used to modify existing signals (Note: these techniques will not work on clocks). The most commonly used technique is the dragging of signal transitions to adjust their location. The other three techniques all act on signal segments, the waveforms between any two consecutive signal transitions. The segment waveform can be changed, deleted, or a new segment can be inserted within another segment. Use each of the following techniques:

1. Move a signal transition: Left click and hold down the mouse button on a signal transition

and drag it to the desired location. A green bar  $\stackrel{\bullet}{\Longrightarrow}$  will appear that follows the mouse cursor. Release the mouse button when the green bar is at the location where you wish to place the transition.

2. Change the state of a segment: A segment is the waveform between two consecutive signal transitions. Click on the segment to select it (a selected segment has a highlighted box

drawn around it \_\_\_\_\_\_). Then click on the State Button of the new state desired.

If you try to select a narrow segment and one of the transitions gets selected, widen the seg-

ment by clicking the Zoom In  $\bigcirc$  button. This button is located on the right hand corner of the button bar.

- 3. **Delete a segment:** Select a segment (see above) and then press the **delete** key on the keyboard.

- 4. **Insert a segment:** Inside a large segment, click and drag to the right or left then release. A new segment will be added in the middle of the original segment. For this operation to work the original segment must be wide enough to be selected.

These techniques will not work on clocks, because clocks have fixed edges and segments. To edit a clock, double-click on a segment of the clock waveform in the *Diagram* window. This causes the *Edit Clock Parameters* dialog box to appear. All clock parameters can be changed in this dialog box. If you cannot double-click on a segment without selecting a transition, zoom in until the segment is large enough.

For more information, read *Chapter 1: Signals and Waveforms* in the Diagram Editor & Universal Features on-line help.

# 7) Adjust Diagram to Match Figure

Now use the above techniques to edit the signals so they have roughly the same transitions as the signals in the figure below. This is not the normal way to create a timing diagram, but it will teach you how to use the editing features of WaveFormer Pro. Make sure you try all the editing techniques.

| 5.60n <mark>.424n</mark> | 0ns  20ns  40ns  60ns  80 |

|--------------------------|---------------------------|

| clk                      |                           |

| Qoutput                  |                           |

| Dinput                   |                           |

Tile the Parameter and *Diagram* windows so that you will be able to see the interaction between the two windows. The *Report* window is not used in this tutorial, so you can minimize it if your screen is small.

- Select one of the **Window** > **Tile** menu options in the timing window.

Adjust the zoom level of the drawing so that only 3 whole clock periods are shown on the screen.

- Click the **Zoom In** or **Zoom Out** buttons, which are located on the right hand corner of the button bar, to show less or more of the waveforms. Zooming can also be performed with the 'Click-and-Drag' method. Simply click in the time bar over the waveforms and drag the cursor to the left or right to zoom out or in, respectively.

## 8) Moving and Reordering Signals

All signals are moved by dragging and dropping the signal's name. When several signals are highlighted and moved as a group, they will reorder themselves according to the order in which they are selected. This ability to quickly reorder signals by the order of selection will help you deal with the large numbers of member signals of buses.

#### Moving a Single Signal:

- 1. Select the signal **clk** by clicking on the name. (A selected signal will be highlighted.)

- 2. Move the mouse cursor near the very bottom of the selected signal. When the mouse cursor changes from a normal arrow to an up/down arrow, click and hold the left mouse button down. A green bar will appear.

- 3. Drag the green bar until it is in between Qoutput and Dinput.

- 4. **Drop** the green bar by releasing the mouse button. Notice that the timing diagram has redrawn itself.

- 5. Try dropping **clk** at the very top and at the very bottom of the diagram. Leave **clk** at the bottom of the diagram.

#### Moving and reordering multiple signals:

- 1. Select **Dinput**, then select **Qoutput** by left clicking on the signal names in that order.

- 2. **Move** the signals to the bottom of the diagram. Notice that **Dinput** is above **Qoutput** because that is the order in which they were selected.

- 3. Select **Qoutput** and then select **Dinput**.

- 4. **Move** the signals to the top of the diagram. Notice that **Qoutput** is above **Dinput**, because the signals were selected in that order. This is a quick way to reorder a large group of signals.

- 5. Return the signals to their original order, (clk, Qoutput, Dinput).

#### 9) The Right Mouse Button

In the next sections we will add delays, setups, and comments to the timing diagram. These objects are added using the right mouse button. The function of the right mouse button is determined by the second group of buttons on the button bar marked DELAY, HOLD, SETUP, TEXT, SAMPLE and MARKER.

| Delay | Setup | Sample |

|-------|-------|--------|

| Hold  | Text  | Marker |

The red or active mode button indicates the current functionality of the right mouse button. To activate a different mode button, click on it.

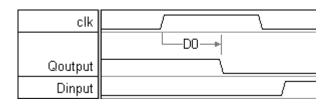

## 10) Add the D Flip-Flop Propagation Delay

Add the delay that represents the propagation time from the positive edge of the clock to the Qoutput of the D flip-flop. To add the delay do the following:

- 1. Activate the **Delay** mode by clicking the **Delay** button.

- 2. Click on the first rising edge of the clock.

- 3. Right-click on the first falling edge of the **Qoutput** signal.

This will draw the D flip-flop delay, and creates a blank delay in the Parameter window.

| name | min | max | margin     | comment |

|------|-----|-----|------------|---------|

| DO   |     |     | na (delay) |         |

When delays are added, they are blank and do not enforce any timing restraints. Notice that the delay is drawn with gray colored lines, this indicates that the delay is not forcing either the min or max edges of the **Qoutput** signal. Now edit the delay's parameters.

- 1. **Double-click** on the parameter name **D0** in the Parameter window to open the Parameter Properties dialog. Adjust the position of the *Parameter Properties* dialog so that you can see the parameter in the *Diagram* window and at least part of the parameter in the *Parameter* window. For simplicity, we will refer to the dialog as *Parameter Properties*, even though the name at the top may say *Delay Properties* or *Setup Properties*.

- 2. Type **5** into the **min** edit box and press the **TAB** key to move to the **max** edit box (leave max blank for now). This enters 5 display time units, or 5ns for this project.

Two things happened when you pressed the TAB key:

- First, the falling edge of Qoutput adjusted itself so that it was 5ns from the clock edge. Measure this for yourself using the time readouts above the signal name window. Left click on the first transition and then move the cursor to the second transition. Notice that the blue readout shows approximately 5ns, depending on the zoom level and the base time unit. The delay can also be made to display the exact distance by choosing the distance choice of the Display label section of the *Parameter Properties* dialog (make sure to return D0 to "Global Default" when you are done experimenting).

- 2. Second, the delay changed from a gray color to a **blue** color. Delays are color coded to indicate which delays are forcing the min and max edges of a transition. This type of critical path display is necessary in diagrams where multiple delays drive a single signal transition. The colors are: Gray = none, Blue = Min only, Green = Max only, Black = both min and max. After this tutorial you may want to experiment with the **multdely.btim** file to see the effects of multiple delays on a single transition and critical path color coding.

Next, finish editing the rest of the parameter. The parameter is named "DFFtp", has a max time of 18ns, and a comment of "Ck to Q propagation time". Use the *Parameter Properties* dialog that is still open to add the following data:

- 1. Click in the **Name** edit box and type **DFFtp** into it.

- 2. Press **TAB** twice so that the **Max** edit box is selected.

- 3. Type **18**. This means 18 display time units, or in this project 18ns.

- 4. **TAB** once so that the comment cell is selected.

- 5. Enter Ck to Q propagation time and press the Enter key.

| Delay Pro | perties                                                |       | _ 🗆 ×   |

|-----------|--------------------------------------------------------|-------|---------|

| Name:     | DFFtp                                                  |       |         |

| Min:      | Б                                                      | Γ     | 5       |

| Max:      | 18                                                     | Γ     | 18      |

| Comment:  | Ck to Q propagation time                               |       |         |

|           | Row 🔽 Change all instances .<br>Ily Subroutine Input . | Corre | elation |

Notice that the DFFtp delay is black which indicates that it is forcing both edges of **Qoutput**. Also notice the falling edge of Qoutput now has a gray uncertainty region. Use the time measure readouts to verify that the edges of the region are 5ns and 18ns from the clock edge (13ns of uncertainty). Double-click on the edge to see the exact edge values.

The *Parameter Properties* dialog is **modeless** (other operations can be performed while the dialog is open) and **interactive** (any changes in the dialog fields are reflected in the diagram after you move out of that field). This tutorial has you open and close it several times so that you learn all the different ways to open the dialog. Also, the tutorial attempts to conserve screen area for laptop users. However, in a normal design you will probably want to keep this dialog open much of the time.

**Tip:** When the Parameter Properties dialog is open you can edit a different parameter by doubleclicking in the *Diagram* or *Parameter* window on the parameter you want to change. If you doubleclick in the *Diagram* window, that instance of the parameter will be edited (the **Change All Instances** checkbox will NOT be checked). If you double click in the *Parameter* window, ALL instances of the parameter will be edited (the **Change All Instances** checkbox will be checked).

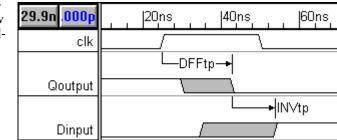

# 11) Add the Inverter Propagation Delay

Add the delay that represents the propagation time of the inverter from its input Q to its output D. To add the delay do the following:

- 1. Activate the DELAY mode by clicking on the delay button.

- 2. Click on the first falling edge of the Qoutput signal (the same edge that ends the "DFFtp" delay).

- 3. Right click on the first rising edge of the Dinput signal.

This will draw the inverter delay, and create a blank delay in the Parameter window. Now let's edit the parameters from the inside of the Diagram window instead of going to the Parameter window.

- Double-click on the new delay in the Diagram Window and enter the following values in the dialog box that appears:

- Name is **INVtp**.

- Min time is **3** ns.

- Max time is **11** ns.

- Comment is **Inverter (Q to D) delay**.

- Click on the **OK** button to close the dialog.

Notice the large uncertainty region for the *Dinput* transition. Click on the first rising edge of **Dinput**, then use the blue delta readout to verify that the uncertainty region lasts for 21ns (13ns from DFFtp + 8ns from INVtp = 21ns). Next, click on the first edge of *clk* and measure to the end of the uncertainty region of *Dinput*. If both the inverter and the D flip-flop are slow, *Dinput* may not transition until 29ns after the clock edge.

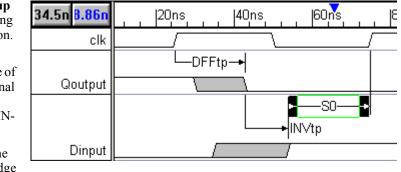

# 12) Add the Setup for the Dinput to Clock

Next add the setup for *Dinput* to clock transition.

- 1. Activate the **Setup** mode by clicking the **Setup** button.

- 2. Left click on the first rising edge of the Dinput signal (the same edge that ends the "IN-Vtp" delay).

3. **Right click** on the second rising edge of the clock.

This will draw the setup parameter. Notice that the arrows of the setup are pointing to the control signal. This means that you added the setup correctly.

Like delays, setups are also created with empty min/max values. They must have a min value before they start to monitor the data signal's position. Now we will edit the setup.

- 1. **Double left click** on the setup name in the Diagram window. This will open the *Parameters Properties* dialog box.

- 2. Enter **Dsetup** into the Name edit box.

- 3. Enter 15 into the min edit box.

| Setup Properties |                             |     | _ 🗆 × |

|------------------|-----------------------------|-----|-------|

| Name:            | Dsetup                      |     |       |

| Min:             | 15                          |     | 15    |

| Max:             |                             |     |       |

| Comment          | Check for metastable condit | ion |       |

4. Enter Check for metastable

condition into the comment edit box.

5. Click the **OK** button to close the dialog.

Notice that the margin column in the *Parameter* window says that there is a **6ns** safety region before the setup is violated. Verify this by clicking on the second rising edge of the clock and placing the cursor on top of the maximum edge of the **Dinput** signal. The blue time readout should say -21ns (setup time 15ns - measured 21ns = -6ns margin).

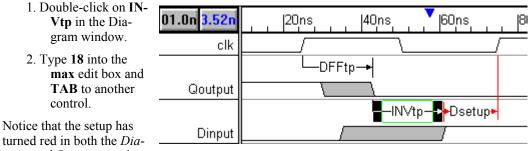

Next, we will demonstrate what happens when a setup is violated. Increase the inverter's delay so that the maximum delay is 18ns instead of 11ns:

gram and Parameter win-

dows. Change the inverter delay back to 11ns and click OK to close the dialog.

#### 13) Add a Free Parameter

So far we have always directly edited a parameter's values. This is inefficient and error prone if the circuit is large. It would be better to define one variable that held the value and make everything that needed that value reference this variable. Then if the value needs to be changed, you only have to edit one variable.

Free parameters act as variables that can be referenced by other parameters. They are called "free" because these parameters are not attached to any signal transitions in the *Diagram* window. Let's add a free parameter to hold the propagation times for the inverter.

#### To add a free parameter:

- 1. Click the **Add Free Parameter** button Add Free Parameter in the *Parameter* window. A blank free parameter is added to the *Parameter* window.

- Double click on the free parameter to open the *Parameter Properties* dialog box and enter (tpFreeInv, 3ns, 11ns, and 74ALS04 inverter delay) for the (name, min, max, and comment cells) of the free parameter.

- 3. Use the **Previous** and **Next** buttons in the *Parameter Properties* dialog to locate the **INVtp** parameter.

- 4. Type **tpFreeInv** into the min and max cells of **INVtp**. Changes to the timing values of the free parameter will now affect INVtp.

| Free Para | ameter Properties        |    |

|-----------|--------------------------|----|

| Name:     | tpFreeInv                |    |

| Min:      | 3                        | 3  |

| Max:      | 11                       | 11 |

| Commen    | t 74ALS04 inverter delay |    |

Note: Free parameters can be saved to special library files which can later be merged into other projects. You can also reference free parameters without including them into your project file by placing libraries in your library search path (**Libraries > Library Preferences** menu option). For more information on free parameters and libraries read the on-line help *Chapter 10: Libraries* or perform the *Parameter Libraries Tutorial*.

# 14) Using Formulas and Constants

Parameters can contain mathematical formulas as well as numeric time values. Legal operations are: multiplication(\*), division(/), addition(+), and subtraction(-). For example, the inverter in this circuit could represent 3 cascaded inverters used to generate a minimum delay of 9ns. To represent this in your timing diagram:

1. Enter the following equation into INVtp's min edit box:

3 \* tpFreeInv

Free parameter names can also be used with an attributed parameter name such as **tpFreeInv.min** and **tpFreeInv.max**. This gives you the flexibility to specify formulas any way you need. If no attribute is added then a min or max is assumed depending on whether the formula is in the min or max column.

#### 15) Summary

Congratulations! You have completed the **Basic Drawing and Timing Analysis** tutorial. In this tutorial we have covered three main topics. The first is how to start a project. Next we covered signals, which includes clocks, signals, and drawing the waveforms of the signals. And finally we covered parameters.

1) Starting a project

- Always set the Base Time Unit one unit below the Display Time Unit to avoid rounding errors. Default values are: Base Units= ps and Display Units = ns.

- 2) Drawing a timing diagram with Signals and Clocks

- Use the Add Clock and Add Signal buttons to add clocks and signals to the diagram. Double left click on the signal name to edit the signal name.

- Left click to draw a waveform with the state of the selected State Button.

- 3) Editing waveforms

- Drag and drop signal transitions.

- To change the graphical state of a segment, select it then press a State Button to indicate the new graphical state.

- To Delete a segment, select it then press the delete key on the keyboard.

- To Insert a segment, left click and drag to the right.

- 3) Timing Analysis with Parameters

- Add delay, setup, and hold parameters by (1) activating the mode button of that name, (2) left clicking on the first signal transition, and (3) right clicking on the second signal transition.

- Edit parameters by double left clicking on the parameter in either the Diagram or the Parameter window.

- Free parameters are variables that other parameters reference. Use the Add Free Parameter button in Parameter Window to add a free parameter.

- To use a free parameter, type the name of the free parameter in the min or max column. Free parameters can also use the dot min/max property to specify a specific value. For example, Inverter.min retrieves just the minimum value of the parameter called Inverter.

# **Interactive HDL Simulation Tutorial**

This tutorial introduces the Interactive HDL Simulation. WaveFormer, VeriLogger and TestBencher Pro have a built-in Interactive HDL Simulator that greatly reduces the amount of time needed to draw and update a timing diagram. Using Boolean and Registered logic equations written in VHDL, Verilog, or SynaptiCAD's syntax you can describe signals in terms of other signals in the diagram. You will no longer have to figure the output of a combinational circuit or calculate the critical path of a synchronous circuit by hand. SynaptiCAD's interactive simulator will generate the HDL code using information entered into the Logic Wizard dialog and then simulate the result. Since the simulator is interactive, changes to input waveforms will automatically re-simulate so that your timing diagrams always reflect accurate design data.

This feature is included in the VeriLogger and TestBencher products even though they have a built in Verilog simulator because it makes generating test benches and timing diagrams so fast that we couldn't hold it back. In WaveFormer, it is the backbone of the timing analysis and design features. The Interactive simulator supports multi-bit equations and true min-max timing. This tutorial contains some examples of equations that are supported.

This tutorial assumes that you are able to draw signals and can add delays, setups, and holds to those signals. We recommend that beginners start with the *Basic Drawing and Timing Analysis Tutorial* to learn the basics of timing diagram editing, before attempting this tutorial.

If you are evaluating Timing Diagrammer Pro and you would like to learn about the simulation features, close the program and restart the evaluation version in WaveFormer Pro mode.

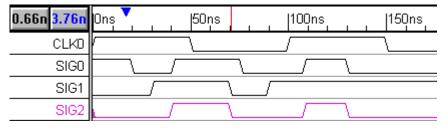

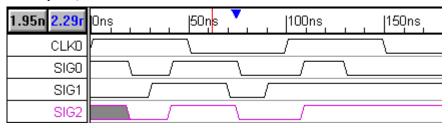

| .000p <mark>99.2r</mark> | Ons 50ns 100ns 150ns |

|--------------------------|----------------------|

| CLKO                     |                      |

| SIGO                     |                      |

| SIG1                     |                      |

| SIG2                     |                      |

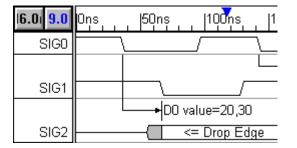

# 1) Interactive HDL Simulation

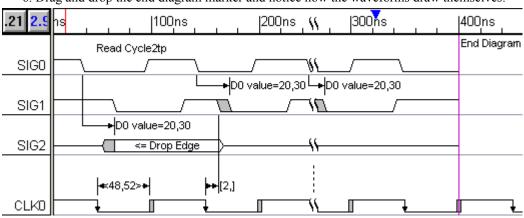

Figure 1.1: Timing diagram used for the Interactive HDL Simulation Tutorial Create a timing diagram for experimenting with the Interactive HDL Simulator:

- 1. Add a clock named CLK0 and accept the default properties of 100ns period.

- 2. Add two signals, SIG0 and SIG1, to the timing diagram.

- 3. Draw the waveforms for signals *SIG0* and *SIG1* so that they resemble the signals in Figure 1.1. These will be the input signals for our simulation.

4. In the Parameter window, click the Add Free Parameter button

Add Free Parameter to add a free parameter **F0** to the *Parameter* window.

- 5. Double-click on the free parameter F0 (in the *Parameter* window) to open the *Parameter Properties* dialog.

- 6. Type 10 in the *Min* edit box and 15 in the *Max* edit box.

- 7. Click the OK button to close the dialog.

- 8. Add signal **SIG2** to the timing diagram. You do not have draw the waveforms now, we will be simulating this signal.

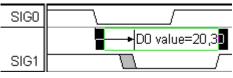

#### 2) Generate Waveforms From Boolean Equations

We will begin by simulating a Boolean Equation. WaveFormer Pro accepts Boolean equations in either VHDL, Verilog, or SynaptiCAD's enhanced equation syntax. The SynaptiCAD format supports the following operators: and or &, or or |, nand, nor, xor or  $^$ , not or  $\sim$  or !, and delay.

The **delay** operator takes a signal on the left, and a time or parameter name on the right, and returns a signal. If a parameter name is used on the right hand side of the delay operator, then the equation will simulate true min/max timing. This true min/max timing is the main advantage that Synapti-CAD's format has over the VHDL or Verilog format.

#### Simulate a Boolean equation:

- 1. Double click the **SIG2** signal name to open the *Signal Properties* dialog. Arrange the *Signal Properties* dialog so that you can see the dialog and the 3 signals at the same time. This dialog is modeless, so leave it open for this entire section. All controls and buttons used in this section are contained in the *Signal Properties* dialog.

- 2. Make sure that the **Boolean Equation** radio button Solean Equation is selected.

- 3. Type the following equation into the Boolean equation edit box (signal names are case sensitive): SIG0 and SIG1

| Boolean Equation: | ex. (SIG1 | and SIG2) delay 5 |  |

|-------------------|-----------|-------------------|--|

|                   |           |                   |  |

SIGO and SIG1

4. Click the **Simulate Once** button and watch the signal draw itself. Notice that SIG2 is the result of the Boolean Equation "SIG0 and SIG1". By default, the **Simulate** radio button is not checked, so if you moved an edge on SIG0, SIG2 is not automatically re-simulated.

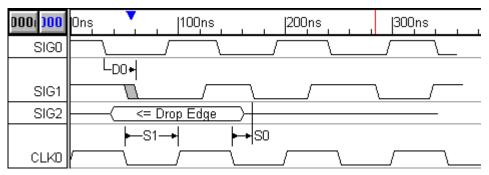

| 40.8n <mark>8.37r</mark> | Ons  50ns  100ns  150ns |

|--------------------------|-------------------------|

| CLKO                     |                         |

| SIGO                     |                         |

| SIG1                     |                         |

| SIG2                     |                         |

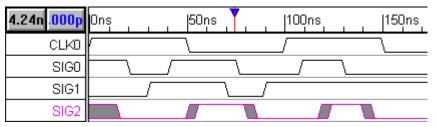

#### **Continuously Simulate the Boolean Equation:**

Enable the Simulate radio button. Notice that the SIG2 is now drawn in purple. This color means that the signal is being continuously simulated, and changes in the input waveforms cause automatic resimulations. If you are using VeriLogger Pro or TestBencher Pro, make sure that the program is in Auto Run simulation mode. Debug Run mode will not continuously update signals. The Auto Run/ Debug Run simulation mode button is located on the simulation toolbar, in the upper left of the window below the Project menu.

2. Move some of the edges on SIG0 and SIG1 and watch SIG2 re-simulate. (Notice that you cannot drag and drop SIG2's signal edges because they are calculated edges).

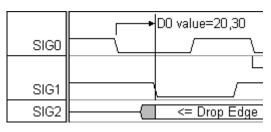

#### 3) Boolean Equations with Delays

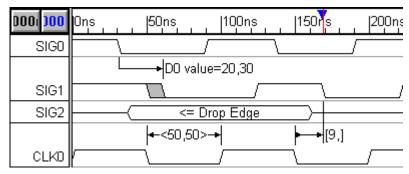

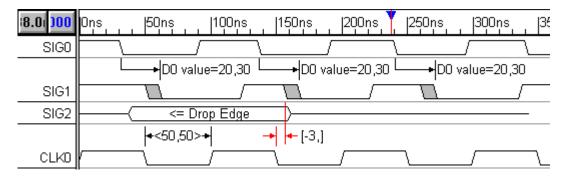

Next we will modify the Boolean equation to take into account the propagation delay through the AND gate. First we simulate a simple 15ns delay, then we will simulate a min/max delay.

#### Simulate a simple delay:

1. Enter one of the following Verilog, VHDL, or SynaptiCAD equations into the **Boolean** Equation edit box of SIG2:

#15 (SIG0 & SIG1)

(SIG0 and SIG1) after 15

(SIG0 and SIG1) delay 15

| 3.31n <mark>.584</mark> r | 0ns   50ns   100ns   150ns |

|---------------------------|----------------------------|

| CLKO                      |                            |

| SIGO                      |                            |

| SIG1                      |                            |

| SIG2                      |                            |

2. Click the **Apply** button and verify that SIG2 is correctly drawn.

#### Simulate a true min/max delay using SynaptiCAD syntax:

Modify the Boolean Equation of SIG2 to take into account the min and max propagation delay of the AND gate. Enter (SIG0 and SIG1) delay F0 into the Boolean Equation edit box. This Boolean Equation references the Free Parameter F0 that you added at the beginning of the tutorial.

2. Click the **Apply** button to cause a simulation. Notice the gray uncertainty regions on SIG2. This true min/max timing is the main advantage that SynaptiCAD's format has over the VHDL or Verilog format.

#### View the HDL code that models the Boolean equation:

1. Click the Verilog or VHDL radio button simulates the Boolean Equation. Native HDL code can be added here to perform a special function (ability to use Native HDL code is only supported for Verilog at this time, not for VHDL). Do not modify the code now. The code should resemble the following example:

```

wire # F0_min SIG2_wf0 = (SIG0 & SIG1 );

wire # F0_max SIG2_wf1 = (SIG0 & SIG1 );

assign SIG2 = (SIG2_wf0 === SIG2_wf1) ? SIG2_wf0 : 'bx;

```

- 2. Click the **Boolean Equation** radio button to display the Logic Wizard section (or Boolean Equation Section) of the *Signal Properties* dialog.

- 3. Leave the Signal Properties dialog open. We will be using it in the next section.

**Note:** This example demonstrated true min/max simulation, however Min-Only and Max-Only simulations can be performed by changing the selection in the **Timing Model** drop-down list of the *Simulation Preferences* dialog box. The *Simulation Preferences* dialog can be opened using the **Options** > **Diagram Simulation Preferences** menu option. The **Timing Model** drop-down list is in the upper right corner.

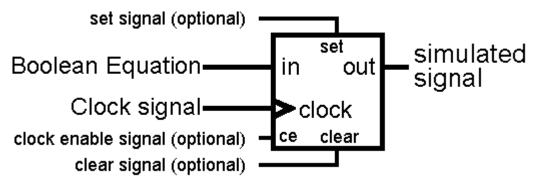

#### 4) Register and Latch Signals

The Interactive Simulator can register or latch the result of a Boolean equation. Figure 1.2 represents the circuit that is modeled.

The *Signal Properties* dialog should still be open and displaying the **SIG2** information from the last section. Let's experiment with the register and latch functions:

1. Enter the equation **SIG1** into the **Boolean Equation** edit box of SIG2.

| Boolean Equation: ex. (SIG1 and SIG2) delay 5 |   |

|-----------------------------------------------|---|

| SIG1                                          | • |

- Click the Simulate Once button to simulate the equation. SIG2 should look like an exact copy of SIG1. When we register SIG2 you can visually compare it to SIG1 to see the effects of the register.

- 3. Next use the **Clock** drop down list box and choose **SIG0** as the clocking signal. The clocking signal can be any clock or signal in the timing diagram (the default value "Unclocked" means no flip-flop is present).

- 4. Next use the **Edge/Level** drop down list box (on the right side of the dialog) and choose **both** as the triggering edge.

| Clock: | SIGO | - |  |

|--------|------|---|--|

|        |      | _ |  |

5. Click the **Simulate Once** button to simulate the circuit. Notice that SIG2 only transitions when SIG0 has a positive or negative edge transition (move some edges on SIG0 and SIG1 to verify this).

Whether a Register or a Latch is simulated depends on the type of triggering in the Edge/Level list box. For a Register circuit choose **neg** for negative edge triggering, **pos** for positive edge triggering, and **both** for edge triggering. For a Latch circuit, choose either **low** or **high** level latching.

6. Choose different Edge/Level values and press the Simulate Once button to verify the operation of the register and latch functions.

## 5) Set and Clear Lines

The **Set** and **Clear** lines are useful when defining circuits whose initial value needs to be specified. In this example we will demonstrate how to design a **divide by 2 circuit** using a negative edge triggered register with an asynchronous active-low set line.

#### To specify the initial value:

- 1. Click the Add Signal button to create a new signal named SIG3.

- 2. Double-click on the SIG3 name to open the Signal Properties dialog.

- 3. Type **!SIG3** into the **Boolean Equation** edit box (it references itself in the Boolean Equation).

- 4. Choose CLK0 from the Clock drop down list box.

- 5. Make sure the Edge/Level setting is set to neg.

- 6. Click the **Simulate** radio button. Notice that the waveform for **SIG3** is completely gray but that the status bar (in the lower right corner of the window) reports **Simulation Good**. This is because **SIG3**'s Boolean equation references itself but it does not provide the simulator with a known start state.

| 7. Click the Advanced                                                                                                                                                                                                                                     |                                                                           |                                                   |                            |                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------|----------------------------|----------------|

| <b>Register</b> button in                                                                                                                                                                                                                                 | Advanced Register a                                                       | and Latch Cont                                    | rols                       | ? ×            |

| the Signal Proper-<br>ties to open the Ad-<br>vanced Register and<br>Latch Controls dia-<br>log. All the register<br>and latch individual<br>propagation times,<br>setup/hold con-<br>straints, clock en-<br>able, and set/clear<br>options are set here. | Set and Clear<br>Active Low<br>Asynchronous<br>Clock Enable<br>Active Low | Clk > Out LH:<br>Clk > Out HL:<br>Setup:<br>Hold: | 0<br>0<br>0<br>0<br>Cancel | ns<br>ns<br>ns |

| Note that Global de-                                                                                                                                                                                                                                      |                                                                           |                                                   |                            |                |

| faults are set using                                                                                                                                                                                                                                      |                                                                           |                                                   |                            |                |

- the **Options > Simulation Preferences** menu.

- 8. Make sure the **Active Low** and the **Asynchronous** check boxes in the *Set and Clear* section are checked. Click **OK** to close the dialog.

- 9. Choose SIG0 in the Set drop down list box of the Signal Properties dialog.

- 10. Click the Simulate Once button. This button is located at the top left corner of the Signal Properties dialog, under the signal name. Notice that SIG3 now has a simulated waveform. Experiment with SIG0 to see how the active low set line affects the operation of the flip-flop. You may want to redraw SIG0 so that it goes low early in the timing diagram, and then stays high for four or five clock cycles.

The **Clock to Out**, **Setup**, and **Hold** edit boxes in the *Advanced Register* dialog accept time values for various timing constraints on the register and latch circuit. For more information on Register and Latch timing, see the on-line help *Chapter 12: Interactive HDL Simulation*.

## 6) Multi-bit Equations

The Interactive Simulator can automatically generate multi-bit equations for the register, latch and combinatorial logic circuits. To convert a register or latch circuit into a multi-bit signal, change the MSB of the input signal and the MSB of the register or latch. If the sizes of the signals do not match, WaveFormer maps as many LSB's as it can.

First setup the diagram to experiment with multi-bit equations:

- 1. Delete the SIG3 signal by selecting it and pressing the Delete key.

- 2. Create a copy of SIG2. Click on the SIG2 name in the Label window to select it. Select the Edit > Copy Signals menu option to copy the signal, then the Edit > Paste Signals option to paste the signal. There are now two signals named SIG2 in your diagram. Rename the bottom SIG2 to SIGX. SIGX should have the exact same waveform as SIG2.

Next, change the output of SIGX to a multi-bit signal:

- 1. Double-click on the SIGX signal name to edit it in the Signal Properties dialog.

- 2. Make sure the **Simulate** radio button is selected.

- 3. Type 3 in the Bus MSB edit box. This will make SIGX a 4-bit signal.

- 4. Click the Apply button. SIGX's waveform is now drawn as a bus with a 4 bit binary display. Only the LSB of SIGX is working because the input signal SIG1 is a single bit. Compare SIG2 and SIGX and verify that they are the same values.

Change the input signal **SIG1** to a multi-bit signal:

- 1. Double-click on the SIG1 signal name to edit it the Signal Properties dialog.

- 2. Change the name of **SIG1** to **SIG1[3:0]**. Changing the name using the bracket notation has the same effect as changing the values in the **MSB** and **LSB** edit boxes.

- 3. Click the **Apply** button to accept the change. Now all four bits of **SIGX** should be toggling 1111 and 0000. If the radix is in **Hex**, the signal will toggle between 0 and F. The radix box is located in the lower left part of the dialog.

If you want to further experiment with multi-bit signals, change **SIG1**'s graphical segments to Valid regions instead of Highs and Lows. Then double click on a valid region to open the *Edit Bus State* dialog box. Type different 4-bit values, like 1010 or 0011, into the **Virtual** edit box and watch how it affects the output of **SIGX**.

Next, set up the diagram for the next section:

- 1. Delete signals SIG1, SIG2, and SIGX by selecting the names and pressing the Delete key.

- 2. Add a signal called SIG1. Do not draw the waveform, we will simulate it in the next section.

- 3. The timing diagram should consist of one clock (CLK0), and two signals (SIG1 and SIG0).

## 7) Experiment with Behavioral HDL Code

In addition to the simulation of Boolean and registered logic circuits, SynaptiCAD products can simulate behavioral HDL code. To enter behavioral code for a signal, click on either the **Verilog** or the **VHDL** button in *the Signal Properties* dialog and type code directly into the edit box.

WaveFormer Pro, VeriLogger Pro and TestBencher Pro also provide a template feature that allows you auto generate the register and latch models used by the Logic Wizard. In this section we will use a register template as a starting point to build a circuit that asynchronously counts the number of edges that occur on **SIG1** and synchronously presents the total number of edges on the negative edge of the clock. To model this circuit:

- 1. Double-click on the SIG1 signal name to edit it in the Signal Properties dialog.

- 2. Select the **Simulate** radio button.

- 3. Choose CLK0 from the Clock drop-down list box.

- 4. Choose neg from the Edge/Level drop-down list box.

- 5. Type **3** into the **Bus MSB** edit box.

- 6. Click the **Verilog** code button to view the resulting template code:

**Note:** the internal wire name SIG1\_wf\*\*\* will vary depending on how many signals you have simulated.

The auto generated variable **PLACEHOLDER** is undefined and will not simulate. If a Boolean equation was defined for the circuit, it would replace the PLACEHOLDER variable. The **registerN**\_Asyn line instantiates (defines an instance of) a 4 bit negative-edge-triggered register of the type used by the logic wizard. This register takes PLACEHOLDER as an input and outputs a synchronized version on **SIG1**.

7. We will use the PLACEHOLDER variable to store the edge count. Edit the behavioral code so that it looks like this (add the bold lines):

```

reg [3:0] PLACEHOLDER;

initial PLACEHOLDER = 0;

always @(SIGO)

PLACEHOLDER = PLACEHOLDER + 1;

wire [3:0] SIG1_wf1 = PLACEHOLDER;

wire [3:0] SIG1_wf0;

registerN_Asyn #(4,1,1) registerN_Asyn_SIG1(SIG1_wf0,CLK0,

SIG1_wf1,1'b0,1'b1,1'b1, $realtobits(0.0),$realtobits(0.0),$re-

altobits(0.0),$realtobits(0.0) );

```

assign SIG1 = SIG1\_wf0;

8. Click the **Simulate** radio button. Verify that SIG1 is counting the edges of SIG0. The new edge count is presented on each negative edge of CLK0.

The code that you just entered is behavioral Verilog code. The first line defines PLACEHOLDER as a 4-bit register. PLACEHOLDER needs to be defined as a register rather than a wire in this case because it must "remember" its value. Verilog wires don't remember their values so they must be constantly driven to retain their value. The second line initializes the value of PLACEHOLDER to 0 when the simulator first runs. The third and fourth lines contain an always block (note for VHDL

users: these work like VHDL process blocks). Whenever **SIG0** changes state, the always block will execute, incrementing PLACEHOLDER. The last two lines consist of the automatically generated template code that instantiates the synchronizing register.

**Tip:** More information on the HDL simulator can be found in *Chapter 12: Interactive HDL Simulation* in the manual and the on-line help. Also the *Advanced Modeling and Interactive Simulation* tutorial demonstrates how to model a complex circuit using external models, behavioral HDL code, and incremental simulation techniques. The HDL Simulation features are different from the VHDL and Verilog testbench generation features which are covered in the Advanced HDL Simulation, VeriLogger Pro, and TestBencher Pro tutorials.

## 8) Summary

Congratulations! You have completed the Interactive HDL Simulation tutorial. In this tutorial we have introduced the use of Boolean Equations and the beneficial features of the Boolean Equation edit box. We examined the generation of waveforms using equations, simulation of delays, and viewing HDL code generated from an equation. We also covered Register and Latched signals, Multi-Bit signals, and editing behavioral code. For more information please refer to the manual or the on-line help.

# **Waveform Generation And Bus Tutorial**

In this tutorial you will learn techniques to quickly generate signals from temporal equations, add equations to existing signals, and create Virtual, Group and Simulated buses. This tutorial assumes that you are able to draw signals and are familiar with the features explained in the previous tutorials. We recommend that beginners start with the *Basic Drawing and Timing Analysis Tutorial* to learn the basics of timing diagram editing, before attempting this tutorial.

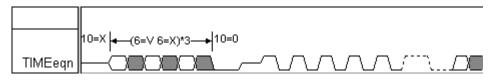

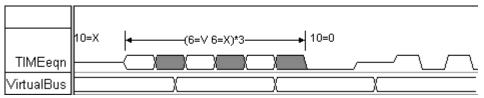

## 1) Generate Waveforms from Temporal Equations

Temporal equations provides a quick way to generate signals that have a known pattern that is more complicated than a periodic clock. Temporal equations are entered in the *Signal Properties* dialog using the edit box to the right of the **Wfm Eqn** button. The edit box contains the default equation: **8ns=Z (5=1 5=0)\*5 9=H 9=L 5=V 5=X**. The default equation draws a waveform that uses all of the available waveform states. If you start by editing the default equation you do not have to memorize the syntax of these equations.

The syntax consists of time-value pairs separated by spaces. The values are 0, 1, Z, V, H, L, and X which represent the graphical states of the waveforms. For example, the **8ns=Z** part of the default equation draws an **8 ns tristate** segment.

To repeat a sequence of states, enclose a list of time-value pairs in parentheses and use the multiply symbol \* followed by the number of times the list is to be repeated. For example (5=1 5=0)\*5, draws five copies of a 5ns strong high segment followed by a 5ns strong low segment.

To experiment with temporal equations:

- 1. Click the Add Signal button to add a signal, and change its name to TIMEeqn using the Signal Properties dialog. (If the dialog is closed, double click on the signal name to open it.)

- 2. In the waveform equation edit box, (to the right of the **Wfm Eqn** button) enter the equation:

10=Z (6=V 6=X) \*3 10=0

3. Click on the Wfm Eqn button to apply the equation.

The 10=Z in the equation means that the signal will be initially tri-stated for 10ns. Next the (6=V1 6=X) will cause the signal to be valid for 6ns then invalid for another 6ns. The \*3 will cause the sequence inside the parentheses to be repeated three times. Finally, the 10=0 will cause the signal to be a strong low for 10ns.

The text in the diagram above is made with a combination of text objects and setup parameters with custom labels. It is used to illustrate the different components of a temporal equation. This is just a quick demonstration of the documentation abilities of the program. For more information on documentation *read Chapter 8: Formatting Timing Diagrams*. You do not have to add the text for this tutorial.

Waveform equations are stored in the waveform equation drop down box, located next to the **Wfm Eqn** button. The equations can be used to create new signals or concatenated to the end of an existing signal.

#### Adding equations to existing signals:

- 1. In the *Signal Properties* dialog, click on the down arrow of the equation drop-down box to display the previous equations.

- Select the default equation 8ns=Z (5=1 5=0)\*5 9=H 9=L 5=V 5=X. You may have to scroll down to find it.

- 3. Click the **Wfm Eqn** button. Notice that the waveform was added to the end of the TIMEeqn signal.

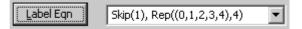

Temporal Equations and a related feature called State Label Equations provide a quick method of generating and then labeling signals that represent Counter and Shifter circuits. The on-line *help Chapter 11: Waveform Equation Generation* has more information on these features.

# 2) Bus Overview

There are three kinds of buses supported by the timing diagram editor: group buses, virtual buses, and simulated buses.

- 2.1 Virtual Buses are normal signals that use extended state information to represent bus values. Virtual buses are added using the Add Signal button. The state information is added using the HEX state button and the Virtual edit box. A virtual bus does not have member signals.

- **2.2 Group Buses** are composite signals whose transitions and state values are determined by their member signals. Instead of individually editing related signals (like the address lines of a part), a group bus can compress all the signals' data into one compact signal. The individual member signals can be uncoupled, or displayed along with the bus. Buses are added using the **Add Bus** button.

- **2.3 Simulated Buses** are similar to group buses. The primary difference is that a simulated bus is purely simulated the member signals cannot be edited manually. When any kind of simulation is performed, the simulated bus will be re-simulated and any changes will take place at that time.

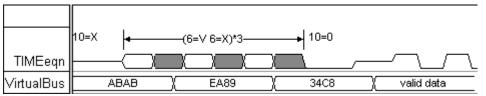

# 2.1) Creating Virtual Buses

Virtual Buses are the recommended way to display and work with bus information. Virtual Buses are also supported by the VHDL and Verilog stimulus and test bench generation features. If timing parameters are attached to a bus then virtual buses will increase computational performance for timing diagrams that use large buses (32 bits or more). To create a virtual bus:

- 1. Click the Add Signal button to add a new signal and name it VirtualBus.

- 2. Click the VAL state button twice, so that it stays active (state buttons will not toggle). The Valid button should be red and have a red T at the top of the button.

3. **Draw** four consecutive valid segments similar to the VirtualBus signal in the figure below.

- 4. Double click on the first segment in the signal to open the Edit Bus State dialog box.

- Enter data into the *Virtual* field and use either the Next and Previous buttons or the key combinations Alt-N and Alt-P to move between the different segments. Any string of characters and numbers can be displayed in the bus. We used the following data: ABAB, E389, 34C8, valid data.

- 6. Click OK to close the Edit Bus State dialog when all the segments have been edited.

- 7. Click the **ZOOM OUT** button a couple of times to demonstrate how the extended state data automatically hides itself when its segment becomes too small to display the text.

- 8. Click the **ZOOM IN** button **S**+ the same number of times to return the diagram to its original zoom level.

When exporting to VHDL or Verilog, the Virtual State information contained in a valid supersedes the graphical state of a segment. This allows you to export the state values of signals with types that have no graphical representation (integers for example).

## 2.2) Creating Group Buses

Use group buses only when you need to get access to an individual bus signal at some point in your design or if you need to compress several signals that already exist. Group buses are useful for analysis of data that is imported from simulators or test equipment. Before a group bus can be created, its member signals must either be specified by selecting the signal names or new signals need to be created. We will use both methods in this tutorial.

To create a group bus and its member signals:

- 1. Make sure that no signal names are selected (clear selected signals by clicking in the *Diagram* window).

- 2. Click on the Add Bus button. This will open the Add Bus dialog box.

- 3. Type **data** into the **Name** box. The member signals will be named the same name as the bus, plus their signal number.

- 4. Enter **0** into the **Start(LSB#):** edit box. This is the least significant bit of the bus.

- 5. Enter 1 into the End(MSB#): edit box. This is the most significant bit of the bus.

- 6. Make sure the **Group Bus** radio button is selected. The radio buttons provide an easy method for creating group or virtual buses.

- 7. Verify that the **Hide member signals** check box is **NOT** checked. We want to be able to see the member signals in this demonstration.

- Click the OK button to create the bus. There should be 3 signals generated: data (the bus), and data0 and

| 1.00r <mark>7.00r</mark> | 0ns  20ns  40ns  60ns  8(      |

|--------------------------|--------------------------------|

|                          | 10=X ← (6=V 6=X) *3 → 10=0     |

| TIMEeqn                  |                                |

| VirtualBus               | ABAB ( E389 ( 34C8 (valid data |

| data0                    |                                |

| data1                    |                                |