**TestBencher Pro**

# **User's Manual**

www.syncad.com

### TestBencher Pro Manual (rev 10.0) copyright 1994-2005 SynaptiCAD

Trademarks

- Timing Diagrammer Pro, WaveFormer Pro, TestBencher Pro, VeriLogger Pro, DataSheet Pro, BugHunter Pro, Reactive TestBench Generation Option and SynaptiCAD are trademarks of SynaptiCAD Inc.

- VERA, OpenVera, VCS, and VCSi are trademarks of Sysnopsys, Inc.

- NC Verilog, NC VHDL, and Verilog-XL are trademarks of Cadence Design Systems, Inc.

- Pod-A-Lyzer is a trademark of Boulder Creek Engineering.

- PeakVHDL and PeakFPGA are trademarks of Accolade Design Automation Inc.

- V-System and ModelSim are trademarks of Model Technology Incorporated.

- Viewlogic, Workview, and Viewsim are registered trademarks of Viewlogic Inc.

- HP and Agilent are trademarks of Hewlett Packard.

- Tektronix copyright Tektronix, Inc.

- PI-2005 and PI-Pat are trademarks of Pulse Instruments.

- Timing Designer and Chronology are registered trademarks of Chronology Corp.

- DesignWorks is a trademark of Capilano Computing.

- Mentor and QuickSim II are registered trademarks of Mentor Graphics Inc.

- OrCAD is a registered trademark of OrCAD.

- PSpice is a registered trademark of MicroSim.

- Windows, Windows NT, and Windows 95/98/2000 are registered trademarks of Microsoft.

All other brand and product names are the trademarks of their respective holders.

Information in this documentation is subject to change without notice and does not represent a commitment on the part of SynaptiCAD. Not all functions listed in manual apply to Timing Diagrammer Pro, WaveFormer Pro, DataSheet Pro, or VeriLogger Pro. The software and associated documentation is provided under a license agreement and is the property of SynaptiCAD. Copying the software in violation of Federal Copyright Law is a criminal offense. Violators will be prosecuted to the full extent of the law.

No part of this document may be reproduced or transmitted in any manner or by any means, electronic or mechanical, including photocopying and recording, for any purpose without the written permission of SynaptiCAD.

For latest product information and updates contact SynaptiCAD at:

web site: http://www.syncad.com email: sales@syncad.com phone: (540)953-3390

# **Table of Contents**

| Table of Contents                                                                                                            | 3  |

|------------------------------------------------------------------------------------------------------------------------------|----|

| Introduction                                                                                                                 | 7  |

| Chapter 1: TestBencher Pro Design Flow                                                                                       | 9  |

| Step 1: Create a New Project                                                                                                 |    |

| Step 2: Add the MUT to the Project                                                                                           |    |

| Step 3: Extract Port Information                                                                                             |    |

| Step 4: Create a Timing Transaction                                                                                          |    |

| Step 5: Define Sequencer Process                                                                                             |    |

| Step 6: Generate the Test Bench                                                                                              |    |

| Step 7: Setting Up Simulators                                                                                                |    |

| Step 8: Simulate Test Bench                                                                                                  |    |

| Chapter 2: Projects and Component Generation                                                                                 |    |

| 2.1 Creating, Opening and Saving Projects                                                                                    |    |

| 2.2 The Project Window                                                                                                       |    |

| 2.3 Sub-Projects                                                                                                             |    |

| <ul><li>2.4 Component Instances of Sub-Projects</li><li>2.5 Component and Component Instance Generation Properties</li></ul> |    |

| 2.6 Signals and Ports for Components                                                                                         |    |

| 2.7 Golden Reference Models                                                                                                  |    |

| 2.8 Libraries and Use Clauses (VHDL only)                                                                                    |    |

| Chapter 3: Transaction Overview                                                                                              | 27 |

| 3.1 Template Diagram and New Transactions                                                                                    |    |

| 3.2 Extracting MUT Ports into a Timing Diagram                                                                               |    |

| 3.3 Transaction Level Variables                                                                                              |    |

| 3.4 Diagram-Level Class Methods                                                                                              |    |

| 3.5 Transaction Architecture                                                                                                 |    |

| 3.6 Diagram Properties                                                                                                       |    |

| 3.7 Diagram Settings Dialog - Overview                                                                                       |    |

| <ul><li>3.8 Diagram Settings Dialog - General Tab</li><li>3.9 Diagram Settings Dialog - Language Specific Tabs</li></ul>     |    |

|                                                                                                                              |    |

| Chapter 4: Transaction Waveforms and Signals                                                                                 |    |

| 4.1 Drawing Transactions for TestBencher                                                                                     |    |

| 4.2 Drawing Waveforms and Bi-Directional Signals                                                                             |    |

| 4.3 Driving Waveform States with Variables                                                                                   |    |

| 4.4 Driving Conditional State Values                                                                                         |    |

| 4.5 Adding Signals<br>4.6 Temporal Expressions for TestBencher                                                               |    |

| 4.7 Controlling the Triggering Order of Parameters                                                                           |    |

| 4.8 Sensitive Edges                                                                                                          |    |

|                                                                                                                              |    |

| Chapter 5: Transaction Delays, Setups, and Holds                                                 | 49 |

|--------------------------------------------------------------------------------------------------|----|

| 5.1 Adding and Editing Parameters                                                                |    |

| 5.2 Delays                                                                                       |    |

| 5.3 Resolving Multiple Delays                                                                    |    |

| 5.4 Setups and Holds                                                                             |    |

| 5.5 Creating Continuous Setups and Holds                                                         |    |

| Chapter 6: Transaction Samples                                                                   | 55 |

| 6.1 Adding a New Sample                                                                          |    |

| 6.2 Sample Condition and Actions                                                                 |    |

| 6.3 Interpreting Sample Conditions and Blocking Points                                           |    |

| 6.4 Samples Triggering a Delayed Transition or Another Sample                                    |    |

| 6.5 Using Sample Variables                                                                       |    |

| 6.6 Storing Sample Values in User Defined Variables                                              | 61 |

| Chapter 7: Transaction Markers                                                                   | 63 |

| 7.1 Adding a Marker to a Diagram                                                                 |    |

| 7.2 End Diagram Markers                                                                          |    |

| 7.3 Pause Simulation Marker (Verilog Only)                                                       |    |

| 7.4 Wait Until Marker                                                                            |    |

| 7.5 Loop Markers                                                                                 |    |

| 7.6 HDL Code Markers                                                                             |    |

| 7.7 Semaphore Markers                                                                            |    |

| <ul><li>7.8 Pipeline Boundary Markers</li><li>7.9 Documentation and Time Break Markers</li></ul> |    |

| Chapter 8: Classes and Variables                                                                 |    |

| 8.1 Class Libraries                                                                              |    |

| 8.2 Classes                                                                                      |    |

| 8.3 Variables                                                                                    |    |

| 8.4 Variable and Class Field Properties                                                          |    |

| 8.5: Language Independent Types                                                                  |    |

| 8.6 Data Packing                                                                                 |    |

| 8.7 Class Methods                                                                                |    |

| 8.8 Constrained Random Number Generation                                                         |    |

| 8.9 File Input and Ouput Variables                                                               |    |

| 8.10 Importing Fields from a Template File                                                       |    |

| 8.11 Semaphores                                                                                  |    |

| Chapter 9: Project Component and Transaction Sequencer                                           | 85 |

| 9.1 Transaction Calls                                                                            |    |

| 9.2 Writing Code in the Template File                                                            |    |

| 9.3 Transaction Manager and Test Reader                                                          |    |

| 9.4 Transaction Generator                                                                        |    |

| 9.5 Transaction Monitor                                                                          |    |

| 9.6 Changing a Project's Template File                                                           |    |

| Chapter 10: Generation and Simulation                    | 93  |

|----------------------------------------------------------|-----|

| 10.1 Generate the Bus Functional Model                   |     |

| 10.2 Simulator and Compiler Settings Dialog              |     |

| 10.3 Project Simulation Properties Dialog                |     |

| 10.4 Simulating the Bus Functional Model                 |     |

| 10.5 Generating Command Files for Third Party Simulators |     |

| 10.6 TestBencher Simulation Modes                        |     |

| Chapter 11: Test Bench Techniques                        |     |

| 11.1 Master and Slave Transactions                       |     |

| 11.2 Waiting for Signal Transitions                      |     |

| 11.3 Burst Mode Transactions                             |     |

| 11.4 Conditionally Moving Signal Edges (Sweep Tests)     |     |

| 11.5 Reading and Writing Serial Data                     |     |

| 11.6 Testing a Counter Model                             |     |

| 11.7 External Model Support                              |     |

| Chapter 12: Language Specific Details                    |     |

| 12.1 Verilog                                             |     |

| 12.2 VHDL                                                |     |

| 12.3 TestBuilder                                         |     |

| Appendix A: Editor Commands                              | 117 |

| Appendix B: Supported Simulators                         | 121 |

| Appendix C: Language Independent Operators               |     |

| Appendix D: License Agreement                            |     |

| TestBencher Pro: Basic Tutorial                          |     |

| 1) Create a Project                                      |     |

| 2) Create the Write Cycle Transaction Diagram            |     |

| 3) Create the Read Cycle Transaction Diagram             |     |

| 4) Create the Initialize Transaction Diagram             |     |

| 5) Modify the Sequencer Process                          |     |

| 6) Generate Test Bench and Simulate                      |     |

| Index                                                    |     |

# Introduction

TestBencher Pro provides designers with a graphical environment for rapidly generating system level test benches composed of cycle-based or time-based bus functional models. TestBencher Pro's graphical interface speeds up test bench development for both expert and novice users. TestBencher generates all of the low-level transaction code, verification code, sequence detection, error reporting and file I/O code. The graphical representation also enhances the ability of engineers to share data across projects, even though new engineers might not be familiar with the details of the test bench design.

#### Learning to use TestBencher

The quickest way to learn how to use TestBencher Pro is to work through the tutorials and to read through *Chapter 1: TestBencher Pro Design Flow*. Advanced features such as constrained random number generation, loops in test benches, generating code from samples, and controlling execution using markers can be found in the later chapters. Some resources to use when learning TestBencher are:

- **On-line Help:** Both the TestBencher and the Timing Diagram Editor manuals are available and cross-reference each other.

- **On-line Tutorials:** TestBencher ships with several tutorials that demonstrate how to create different types of bus-functional models. There are also several timing diagram editor tutorials.

- Test Bench Examples: Several test bench examples ranging from simple test benches to PCI and ARM bus examples are located in the *Examples* subdirectory of the installation directory.

- Context Help: Many of the dialogs that you will use contain a context help feature that will allow you to learn more about the specific controls within the dialog. The dialogs with this feature have a small button with a question mark ? in the upper right hand corner of the dialog (next to the close window button). To use context help, click the question mark, and then click the item in the dialog about which you would like to see help.

- Test Bench Techniques: *Chapter 11* of the manual catalogs techniques for generating models with different types of functionality.

Additional information regarding the architecture and design flow of TestBencher Pro is available at the SynaptiCAD website (**www.syncad.com**).

#### 8 Introduction

# **Chapter 1: TestBencher Pro Design Flow**

This chapter will cover the basic design flow for generating a bus-functional model using TestBencher Pro. First you will create a new project file and add information about the model under test (MUT) files. Next you will create the timing diagrams that generate the reusable timing transactions. Then you will edit the top-level model and define the sequence for applying the transactions to the MUT. Finally you will simulate the test bench.

# Step 1: Create a New Project

Projects represent bus functional models (BFM) in TestBencher. They hold all the information needed to generate the entire BFM including the transaction diagrams, top-level file, and the code generation settings. Projects can be included hierarchically in other projects. This allows TestBencher to support multiple BFM component instantiation. Once a project has been completed, the entire bus functional model that it represents, or project component, can be instantiated in another project. *Chapter 2: Projects and Component Generation* has detailed information about creating projects, but essentially when you create a new project you set the name, language, and clocking options for the new BFM.

To create a project:

- Select the Project > New Project menu option. This will open the New Project Wizard dialog.

| New Project Wizard  |                                         | ? ×  |

|---------------------|-----------------------------------------|------|

| Project Name:       | sweeptest2                              |      |

| Project Directory:  | C:\SynaptiCAD\project\                  |      |

| Project Location:   | C:\SynaptiCAD\project\sweeptest2\       |      |

| ļ                   | Transaction-based Test Bench Generation |      |

| -Project Language S | _                                       |      |

| Project Language:   | Verilog                                 | tion |

|                     |                                         |      |

|                     | Cancel Prev Next Finis                  | ;h   |

- The **Project Name** will be both the name of the project and the directory where the project is stored.

- The Language drop down list defines the generated language for the model. Certain features, such as valid signal types, are dependent on the generated language so this option affects the operation of TestBencher. If you are using Verilog and want to enable constrained random number generation, check the Enable TestBuilder Integration checkbox.

- Check the **Transaction-based Test Bench Generation** to make TestBencher generate bus-functional models instead of single diagram test benches.

- Click the Next button to move to the next dialog.

| New Project Wizard ? 🗙                                            |  |  |  |

|-------------------------------------------------------------------|--|--|--|

| Original Template: C:\SynaptiCAD\templatefiles\tbench.v           |  |  |  |

| New Template: C:\SynaptiCAD\project\sweeptest2\sweeptest2.v       |  |  |  |

| Component Model Name: sweeptest2                                  |  |  |  |

| Default Clock: SysClock  Create Default Clock Generator Edge: pos |  |  |  |

| Default Diagram Settings Cancel Prev Mext Einish                  |  |  |  |

- If your project is clocked, then type in the name of the clocking signal.

- Click the Default Diagram Settings button to edit the default diagram settings for new diagrams. By default, the Include Delay Time setting is not enabled for your design. See Section 3.9: Diagram Settings Dialog Language Specific Settings for information about how this setting is used.

- General

Verilog

VHDL

TestBuilder

Default Delay After Clock Edge

O As Drawn

Image: Fixed

0

ns

- Click the **Finish** button to close the *New Project Wizard* and create the new project.

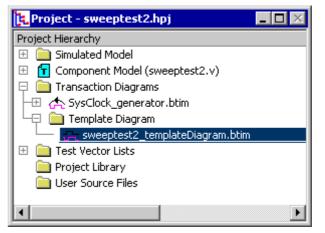

Notice that TestBencher automatically opens the *Project* window (see *Section 2.2: The Project Window*) and populates it with the top-level template file (see *Chapter 9: Project Component Sequencer Files*) and template diagram (see *Section 3.1: Template Diagram and New Transactions*). The template diagram is the starting point for any new transactions that you add to the project. The *Project* window will be your main resource for navigating through the different parts of the bus functional model.

## Step 2: Add the MUT to the Project

The Model Under Test, MUT, files of the design should be added to the project. TestBencher will use these files to extract the signal and port information for use in the transaction diagrams and will use the file information to build make files for your simulator.

To add a source file to the project:

- Right-click in the User Source Files folder in the Project window to open the context menu, and select the Add Files to User Source File Folder menu option

- OR, choose the Project >Add Files menu option

| User Source Files | Add Files to |

|-------------------|--------------|

|                   | Add Flies to |

dd Files to User Source File Folder....

- Both of these functions open a file dialog. Select the files that you would like to add to the project and click the **Open** button to close the dialog. All files necessary to compile and simulate the MUT should be added to the project because TestBencher parses the entire design.

Notice that the file names are listed in the *User Source Files* folder in the *Project* window. The source code can be viewed by double-clicking on the file name.

# **Step 3: Extract Port Information**

The next step is to build the MUT and extract the port information from it. TestBencher will parse the MUT and display the hierarchy

of the design in the *Project* window. Also, the top-level ports or signals if there are no ports, will be inserted into current timing diagram.

To parse the source files and build the MUT:

- Double-click the diagram template file to open the timing diagram.

- Click the Extract Ports From MUT but-

ton for the *Simulation Button Bar*. This will cause the source files to be parsed and the components to be built.

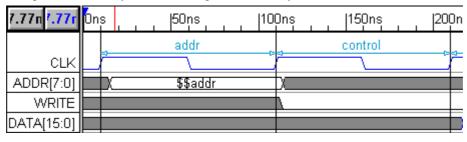

- Notice that the signal and port information has been added to the template diagram.

Click the **Save** button **b** or choose the **File > Save Timing Diagram menu item** to save the template diagram.

- Notice that the *Simulated Model* folder in the *Project* window displays design hierarchy.

| 🔁 Project - sweeptes                          | t2.hpj*    | _ 🗆          | ×               |

|-----------------------------------------------|------------|--------------|-----------------|

| Project Hierarchy                             |            |              | ▲               |

| 📮 🚞 Simulated Model                           |            |              | ماResults.b     |

| -== <u>M <sram></sram></u>                    | Diagram    | n - sweepte: | st2_templateDia |

|                                               | Add Signal | Add Bus      | Delay Setup S   |

| WRB                                           |            | Add Spacer   | Hold Text 1     |

| ABUS                                          | 72.70ns    | 72.70ns      | Ônș             |

| 🛛 🗌 🦢 🔶 DBUS                                  |            | Pue Classic  |                 |

| 🛛 🗠 🔂 🖬 Variables                             |            | SysClock     |                 |

| 🛛 🕂 🚰 Stimulus & Re                           | CSB        |              |                 |

| └── 📋 simulation.log<br>└── 🧰 Utilities Files | WRB        |              |                 |

| Component Mod                                 | ABUS[11:0] |              |                 |

| 🕀 💿 Class Library                             |            | DBUS[7:0]    |                 |

*Chapter 3: Transaction Overview* has more information about creating internal signals for the diagrams and manually editing the signal type, direction, and size.

# Step 4: Create a Timing Transaction

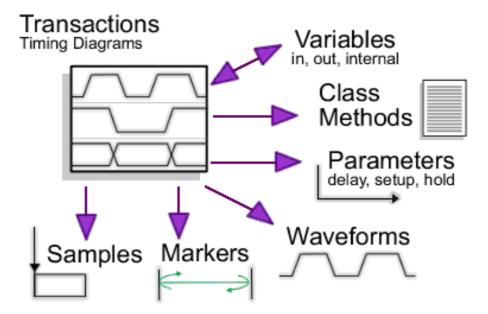

A timing transaction is a timing diagram that represents a reusable interface specification of the bus-functional model that you are creating (e.g., read cycle, write cycle, interrupt cycle). Timing diagrams are created using the built-in timing diagram editor. The tutorials and *Chapters 3-7* describe how to draw the timing diagrams and control the generated code.

New timing diagrams that are created while this project is active will have the same properties and signals as the *Template Diagram*. This diagram is located in the *Template Diagram* folder in the *Project* window. Any signals that will be in all your timing diagrams (such as a global clock signal, or the ports for the MUT) should be in this diagram.

| 😫 Project - sweeptest2.hpj* 📃 🗖 🔀  |

|------------------------------------|

| Project Hierarchy                  |

| 🗄 🧰 Simulated Model                |

| 🗄 🚹 Component Model (sweeptest2.v) |

| 🗄 🧰 Transaction Diagrams           |

| 🗄 🦲 Test Vector Lists              |

| 🦲 Project Library                  |

| 📮 🦲 User Source Files              |

| 🕀 🔄 sram.v                         |

|                                    |

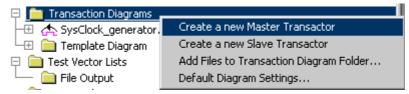

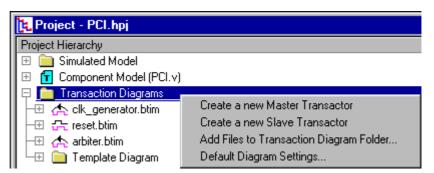

To draw a timing transaction:

- In the Project window, right-click on the Transaction Diagrams folder and choose either Create a new Master Transactor or Create a new Slave Transactor from the context menu. This opens a file dialog to create and save the diagram. After closing the dialog, a new diagram is created using the same properties and signals as the Template Diagram that you modified in Step 3: Extract Port Information. Slave diagrams run in a looping mode until they receive an abort call, and Master diagrams run once and stop.

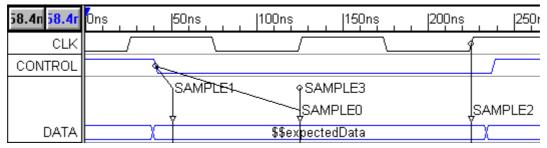

- Create a timing diagram by sketching the waveforms using the *Timing Diagram Editor*. Optional components such as samples, markers, delays, variables, and class methods will be discussed in more detail later in this manual and are demonstrated in the tutorials. The optional components needed are determined by the needs of the test bench.

- Select the File > Save Timing Diagram menu option to save the timing diagram and generate the HDL code. Each time you save a timing diagram new code is generated for it.

- By default a timing diagram will generate Master Transaction code that will run once and then stop. To generate Slave Transaction code that will loop continuously you just need to change the diagram setting to slave: right click on the timing diagram name in *Project* window and choose **Diagram Settings** (see *Section 3.7: Diagram Settings Dialog Overview*) and then check the **Slave Transactor** radio button.

Source

Code

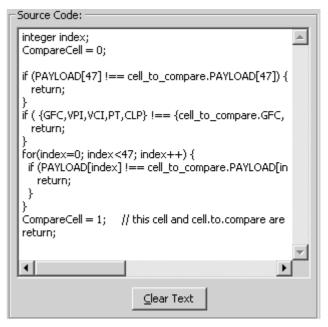

To view the generated HDL source code:

- Click the **Source Code** button to open an editor and view the code. Because the source code is generated for each timing diagram, it should not be edited. It is, however, useful to see how the low level code changes based on the constructs that are placed in the diagram.

At this point you can either design additional transactions, or you can continue with the next few steps and design the top-level test bench. By working with the top-level test bench early in the design you will be able to test individual transactions before constructing the entire bus-functional model.

## **Step 5: Define Sequencer Process**

The top-level template file represents the Component Model. The Component Model controls the execution sequence and monitors the status of each timing transaction in the project. It is also where the model under test is instantiated and connected to the test bench model.

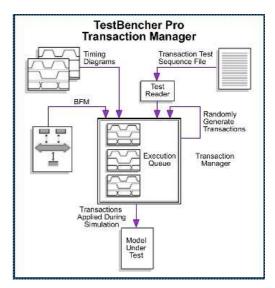

Inside the top-level file is a Sequencer Process that controls the order and logic in which the timing transactions are applied to the model under test. Inside the sequencer process is the place that you will write the system level code to apply the transactions. In addition to the sequencer process, TestBencher can also generate an advanced Transaction Manager that can read transactions from files, randomly generate transactions, or accept transactions posted by the components in the project. *Section 9.6: Changing a Project Template File* describes the sequencer process, transaction manager, and the template file in detail.

Use the *Insert Diagram Call* dialog to add timing diagram apply statements to the Component Model's Sequencer Process:

- Double-click on the Component Model folder in the Project window to open the template file.

- Scroll down in the template file until you find the Sequencer Process. A comment block in the code will help to locate this process. The comment will contain the following text:

// apply transactions to the model under test using:

- Click in the *Editor* window just below this comment. Then right-click and select the **Insert Diagram Calls...** menu option from the context menu. This will open the *Insert Diagram Calls* dialog with a list of statements that represent each of the timing transactions that have been added to the project.

| Insert Diagram Subroutine Call                                                                                | ? ×          |

|---------------------------------------------------------------------------------------------------------------|--------------|

| Apply_tbglobal_clock_looping_nowait;                                                                          |              |

| <b>☆ tbglobal_clock;</b><br>군 tbread(addr, data, delay0_min_bits);<br>군 tbwrite(addr, data, delay0_min_bits); |              |

| Run Mode<br>O Apply                                                                                           | Insert Close |

- Select a timing diagram name. The *Run Mode* radio buttons will default to **Apply** for Master transactions to run them in a blocking mode. For Slaves the default is **Apply-nowait** to run the transaction concurrently with subsequent apply calls.

- Choose a *Run Mode* radio button and press the **Insert** button.

- Notice that the Apply statement was inserted at the same line as your cursor. The *Insert Diagram Call* dialog is a modeless dialog it can remain open while you perform other actions. Inserting additional Apply statements causes those statements to be added on successive lines.

- If any of the applied transactions contain variables, then edit the Apply call to provide values for variable names. In the example Apply statement below, a value of hex 55 is assigned to addr.

// Apply\_tbwrite(addr, data, delay0\_min\_bits)

Apply\_tbwrite('h55, 'hee, \$realtobits(delay0));

Chapter 12: Language Specific Details has more information about language specific features of editing parameter variables.

#### Step 6: Generate the Test Bench

Once the Sequencer Process has been edited, the test bench is ready for generation. This step will expand a series of macros in the template file. Any code that is between the begin and end statements of a macro will be destroyed and re-generated. Any code outside of the macros, such the body of the Sequencer Process will be preserved. *Chapter 10: Generation and Simulation* describes the generation process.

To generate the test bench:

- Click the **Generate Test Bench** button **TB** on the simulation button bar. This expands the macros in the template file.

- Check for generation errors by looking at the **waveperl.log** file in the *Report* window. If there are no errors then you are ready to simulate the BFM.

| 🚍 Report - waveperl.log 📃 🗖 🔀                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Generating Transactors<br>C:\src\install\Examples\Verilog\SweepTest2\SweepTest2_tbg.<br>Warning: Setup doesn't have a min OR max value specified<br>C:\src\install\Examples\Verilog\SweepTest2\SweepTest2_tbre<br>C:\src\install\Examples\Verilog\SweepTest2\SweepTest2_tbw:<br>Generating Component Model Files<br>C:\src\install\Examples\Verilog\SweepTest2\tb_SweepTest2_<br>C:\src\install\Examples\Verilog\SweepTest2\tb_SweepTest2 |

| Number of Warnings: 1                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Done                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| simulation_vlogcmd.log { waveperl.log { Breakpoints { Errors { Differences { Grep {                                                                                                                                                                                                                                                                                                                                                       |

During the Generate Test Bench process several files are generated and they depend on the generation language (see *Chapter 12: Language Specific Details* for more information). All of the generated files are displayed in the *Project* window.

# **Step 7: Setting Up Simulators**

TestBencher Pro needs to know where your VHDL/Verilog simulator or C++ compiler is located. If you are using VeriLogger Pro you can skip this section because the simulator was setup during installation.

The *Simulator/Compiler Settings* dialog contains the path settings for external tools. These settings are saved in the syncad.ini file each time the program is closed. To specify the path for each simulator or compiler that you will use:

- Choose the Options > Simulator / Compiler Settings menu option to open a dialog of that name.

| Simulat  | or / Compiler Settings                             | ? ×                         |

|----------|----------------------------------------------------|-----------------------------|

| _ Simula | tor / Compiler:                                    |                             |

| Tool:    | VeriLogger Command Line 💽 Filt                     | ered by Language: All Tools |

|          | ModelSim Verilog GUI                               |                             |

|          | ModelSim VHDL GUI<br>ModelSim VHDL Command-Line SE |                             |

| Circulat | ModelSim VHDL Command-Line XE,PE                   | I                           |

|          | veniog-xL                                          | _                           |

| Targe    | VeriLogger Command Line                            | On Remote Host              |

|          | NC Verilog                                         |                             |

| Simula   | NC VHDL<br>Microsoft C/C++ (cl.exe)                |                             |

- In the Tools drop-down choose your simulator or compiler.

- In the **Simulator Path** edit box either type in the path name or use the **browse button** to search for the path.

- Continue to setup the paths for each tool that you are interested in using. When you are done click **OK** button to close the dialog.

Each of the main simulation languages has a default tool and program settings that are stored in the Project file. When you create a new project, the *project language* will determine which tools are used. Specify which tool to use and its' default settings:

| - Choose Project > | Project Simulation Pr | operties menu optio | on to open the Pro | ject Simulation Pro | operties dialog. |

|--------------------|-----------------------|---------------------|--------------------|---------------------|------------------|

|--------------------|-----------------------|---------------------|--------------------|---------------------|------------------|

| Project Simulation Properties : SweepTest2 ? 🗙                                                   |

|--------------------------------------------------------------------------------------------------|

| Settings                                                                                         |

|                                                                                                  |

| Configurations: Debug 💽 Add Rename Delete                                                        |

| Settings Configuration                                                                           |

| General Verilog VHDL TestBuilder                                                                 |

| Simulator Type: VeriLogger Command Line Simulator Settings                                       |

| Include Directories: Active-HDL Verilog<br>ModelSim Verilog Command-Line<br>ModelSim Verilog GUI |

| Library Directories: NC Verilog                                                                  |

| Library Extensions: .v;.vo O Min O Typical O Max                                                 |

- Choose the **Settings Template** radio button to indicate that you will be editing the default project settings for all future projects. These settings are saved in the INI file.

- Click on the language tab for the external tool that you are setting up.

- From the Simulator Type drop-down, choose the external tool.

- Choose the **Diagram Settings** radio button and edit the simulator that is used to simulate individual transactions (simulated signals in a *Diagram* window). By default this is setup to use an internal Verilog simulator, but if you are simulating in a different language set the simulator to your external simulator.

- Press the **OK** button to close the dialog.

#### Step 8: Simulate Test Bench

TestBencher Pro ships with a basic version of BugHunter Pro a graphical debugger that can control external simulations. For comprehensive instructions on BugHunter read the BugHunter manual.

Start a simulation:

- Click the **Compile the Active Project button** on the simulation button bar.

- In the *Report* window, check compile error in the simulation results file tabs. If there are no errors then continue.

- Either click the green **Run** button  $\triangleright$  on the simulation button bar or press the <F5> key.

| 🛛 Auto Run 🔄 Verilog 💽 🊰 MAKE 🛛 🔃 🕨 🕨 🖬 🔳 |  |

|-------------------------------------------|--|

|-------------------------------------------|--|

View Simulation Results:

- When the simulation is complete the waveform results will be placed in the *Diagram* window. The simulation output will be displayed in the *Report* window.

16 Chapter 1: TestBencher Pro Design Flow

# **Chapter 2: Projects and Component Generation**

TestBencher Pro uses a project file to represent and to control the generation of a bus-functional model (BFM) component. The information in the project file is displayed in the *Project* window. Context sensitive menus provide a list of actions that can be performed for the elements in the project tree.

Multiple test bench components can be made by including a project inside of another project, and then instantiating the subproject. This allows complex test benches to be developed and verified in an incremental manner. This method also supports multiple port testing.

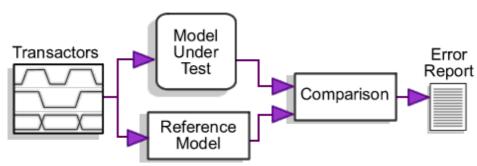

TestBencher can also generate a C++, VHDL or Verilog Golden Reference model that runs in parallel with the VHDL or Verilog Model Under Test. During simulation transactions are sent to both the MUT and the reference model. The results from the two models are then compared.

# 2.1 Creating, Opening and Saving Projects

Projects are created, opened, saved, and closed using the Project menu options.

- Select the Project menu option and choose one of the project submenus: New Project, Open Project, Save Project, or Close Project.

- The New Project menu option opens the New Project Wizard dialog that steps through the process of creating a new project.

The New Project Wizard pane one:

| - <b>Project Name</b> will be the               |                                                             |                     |

|-------------------------------------------------|-------------------------------------------------------------|---------------------|

| name of project and the                         | New Project Wizard                                          | ? ×                 |

| subdirectory that the<br>project will be stored | Project Name: TBSram                                        |                     |

| in.                                             |                                                             |                     |

| - Project Directory con-                        | Project Directory: C:\Program Files\SynaptiCAD\project\     |                     |

| tains the path for the<br>base directory of the | Project Location: C:\Program Files\SynaptiCAD\project\TBSra | am),                |

| project.                                        | ✓ Transaction-based Test Bench Generatio                    | n                   |

| - <b>Project Location</b> displays              | Project Language Settings                                   |                     |

| the complete path to the project file.          | Project Language: Verilog 🔽 Enable Test                     | Builder Integration |

| - Project Language con-                         |                                                             |                     |

| trols the test bench generation language.       | <u>C</u> ancel <u>Prev</u>                                  | xt <u>E</u> inish   |

| The available language                          |                                                             |                     |

| selection is based on your                      | TestBencher License file                                    |                     |

- Enable TestBuilder Integration enables C++ code generation for Verilog projects. This adds many advanced language features, such as constrained random number generation.

- Transaction-based Test Bench Generation check box enables the generation of the multi-transaction based bus-functional model generation. If you uncheck this TestBencher will generate single diagram test benches.

Click the Next button to view pane two of the New Project Wizard:

-The **Template** edit boxes specify the original and new (copied) template file names. The new template file will serve as the top-level source file for the test bench. This file is where the Component Model is generated. A default original template file name is provided, but you can create your own template files. (*Chapter 9: Project Component and Transaction Sequencer* has information on editing and changing the template file).

| New Project Wizard                                                    | ? ×                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Original Template: C:\Program Files\SynaptiCAD\templatefiles\tbench.v |                                                                                                                                                                                                                                                                                    |

| New Template: C:\Program Files\SynaptiCAD\project\TBSram\TBSram.v     |                                                                                                                                                                                                                                                                                    |

| Component Model Name: TBSram                                          |                                                                                                                                                                                                                                                                                    |

| Default Clock: GClock 💽 🔽 Create Default Clock Generator              |                                                                                                                                                                                                                                                                                    |

| Edge: pos 💌                                                           |                                                                                                                                                                                                                                                                                    |

| Default Diagram Settings Cancel Prev Next Ein                         | ish                                                                                                                                                                                                                                                                                |

|                                                                       | Original Template:       C:\Program Files\SynaptiCAD\templatefiles\tbench.v         New Template:       C:\Program Files\SynaptiCAD\project\TBSram\TBSram.v         Component Model Name:       TBSram         Default Clock:       GClock       ✓         Edge:       pos       ▼ |

level projects. Sub-projects usually receive their clocks from the parent projects.

- The **Default Diagram Settings** button opens the *TestBencher Diagram Settings* dialog which is used to set up the default diagram settings, such as verbose code generation. This dialog is discussed in *Section 3.7 Diagram Settings Dialog - Overview*.

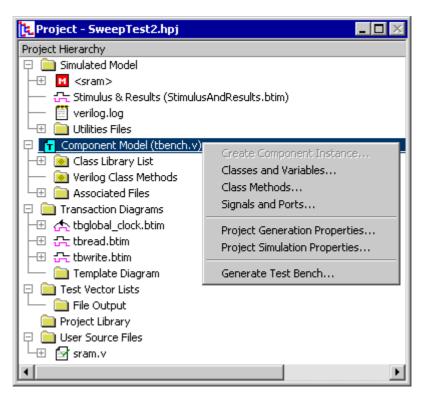

## 2.2 The Project Window

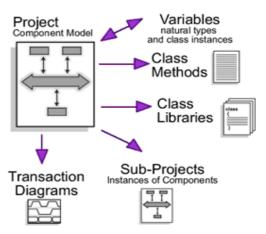

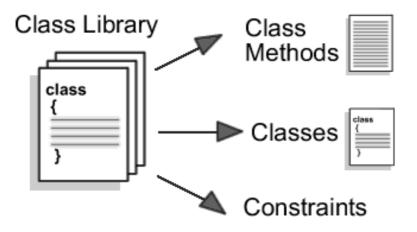

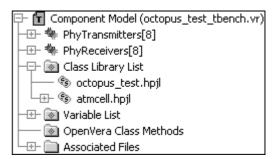

The *Project* window displays all of the different elements of the bus-functional model and the user source code (MUT). This includes all of the available transaction diagrams and sub-projects that can be used in the top-level Component Model. It also displays the project level variables and classes.

The basic controls of the *Project* window are as follows:

- Right click on any node in the Project tree to open a context sensitive pop-up menu that contains all of the operations that can be done to that particular node type.

- Double left click on any node to perform the default action for that node (usually open that file or object in an appropriate editor).

- To expand or hide branches of a tree, click ⊕ or ⊡.

- Drag and drop the column headings to resize columns.

Several folders are created in each project and are used to organize files and objects at the different levels of the test bench. Each of these folders will be discussed at different points in the manual. As an overview:

- Simulated Model folder contains the compiled Model Under Test and the *Stimulus & Results* diagram. See *Chapter 10: Generation and Simulation* for more information.

- **Component Model** is the top-level template file for the test bench. The folder contains all of the project-level classes, variables, class methods, and instances of sub-projects. See *Chapter 9: Project Component and Transaction Sequencer* for more information.

- **Transaction Diagrams** folder contains the template timing diagram and the timing diagrams that have been added to the project, and their associated source code files (in the level beneath the timing diagram). See *Chapter 3: Transaction Overview* for more information.

- Test Vector Files folder contains input and output test vector files. See *Chapter 8: Classes and Variables* for more information.

- **Project Library** folder holds any sub-projects that may be instantiated within the current project. *Section 2.3: Sub-Projects* discusses this folder.

- User Source Files folder contains source files for use in the test bench. Files with a green checkmark icon have been compiled into the test bench; files with a red X icon have not yet been compiled. *Section 3.2: Extracting MUT Ports into a Timing Diagram* has more information.

# 2.3 Sub-Projects

TestBencher Pro supports hierarchical BFM design by allowing projects to be instantiated inside other projects. This lets you develop and verify complex test benches in an incremental manor. For example, if you are designing a test bench for an ATM switch, you can develop a project that can transmit an ATM cell to an interface port on the ATM switch. After you have tested your transmitter project, you can make it a sub-project and instantiate a copy of it for each different port of the ATM switch.

To use a sub-project you first add the sub-project to the **Project Library** folder in the *Project* window and then edit the default signal mappings that will be used when the sub-component is instantiated. *Section 2.4* covers the sub-project instantiation and port mapping.

Add a sub-project to the Project Library folder:

- Right Click on the **Project Library** folder and choose the **Add Sub-Projects** menu option. This opens a file dialog that lets you browse for projects. After you close the dialog, a sub-project with a red chip icon is added to the folder.

- Note the sub-project can be modified while the owning project is open, by expanding the sub-project tree. The sub-project will remain an independent project that can be opened and edited alone, as well.

| 🔁 Project - PCI.hpj         |                       |  |  |  |

|-----------------------------|-----------------------|--|--|--|

| Project Hierarchy           |                       |  |  |  |

| 🗄 📄 Simulated Model         |                       |  |  |  |

| 🗄 🚹 Component Model (PCI.v) |                       |  |  |  |

| 🗄 🗄 🚞 Transaction Diagram   | IS                    |  |  |  |

| 🗄 📄 Test Vector Lists       |                       |  |  |  |

| 📮 🚞 Project Library 💡       |                       |  |  |  |

| 🕂 🕂 🗰 C:\Program Files      | Add Sub-Projects      |  |  |  |

| 🗆 🕂 🗰 C:\Program Files      | Save All Sub-Projects |  |  |  |

Once you add the sub-project, you will need to setup the signals to be exported and the default mapping names for the component. To edit the default signal mappings

- Right-click on the sub-component (red chip icon) and choose **Signals and Ports** from the context menu. This opens the *Component Model Signals and Ports* dialog.

- Create ports for the sub-project by selecting signals in the *Component Signals (Internal)* section and clicking the **Make Internal/Add to Port List** button. This will move the signals up to the *Component Ports (exported signals)* section. Signals can also be dragged from one list to the other.

- Double-click on cells in the **Default Port Mapping** column and either type in a name or select a mapping signal name. Since the sub-project is not the real component you can type in partial names. For example if you plan to connect each instantiation of the sub-project up to a different port of the MUT with port names like *signame0* and *signame1*, a good partial port name would be *signame*. That way, after you instantiate the components you will only have to add the port numbers to the signal names.

|        | Signals<br>CLK<br>FRAMEn<br>AD<br>CBEn | 0<br>0<br>31 | Lsb<br>0<br>0 | 4_state<br>4 state | input             | Default Port Mapping<br>CLK |  |

|--------|----------------------------------------|--------------|---------------|--------------------|-------------------|-----------------------------|--|

| 2<br>3 | AD                                     | -            | -             | 4 ctate            |                   | Leev.                       |  |

| 3      |                                        | 31           | -             | TT_State           | input             | FRAMEn                      |  |

| -      | CBEn                                   |              | 0             | 4_state            | inout             | AD                          |  |

| 1      |                                        | 3            | 0             | 4_state            | input             | CBEn                        |  |

| T      | IRDYn                                  | 0            | 0             | 4_state            | input             | IRDYn                       |  |

| 5      | TRDYn                                  | 0            | 0             | 4_state            | output            | TRDYn                       |  |

| 6      | DEVSELn                                | 0            | 0             | 4_state            | output            | DEVSELn                     |  |

| 7      | STOPn                                  | 0            | 0             | 4_state            | output            | STOPn                       |  |

|        |                                        |              |               | Make Int           | ernal / Add to Po | ort List                    |  |

| lomp   | onent Signals                          | s (not exp   | orted):       |                    |                   |                             |  |

|        |                                        |              | Msb           | Lsb                | Data Type         | Direction                   |  |

|        | Signals                                |              | PISD          | 230                | baca ()po         | En estaten                  |  |

## 2.4 Component Instances of Sub-Projects

Projects listed in the **Project Library** folder can be instantiated and used by the containing project. When a sub-project is instantiated, TestBencher will generate a component instantiation in the top-level template within the *\$TBSubComponentInstantiation* macro and make all of the transaction diagrams of the sub-project available to the owning project. The owning project can call the transactions of each instance of a sub-project. This is discussed in *Section 9.1: Transaction Calls*.

Create a Component Instance of the sub-project:

- Right-click on the sub-project node and select **Create Component Instance** from the context menu option. This will open the *Create Component Instance* dialog.

- Notice that by default the name of the selected **Owning Project** is the immediate parent project of the sub-project to be instantiated. The owning project can be changed using the drop-down list box. The **Instance of** drop down allows you to change the sub-project that will be instantiated.

- Enter the Instance Name to use in the instantiation of the Project Component.

| Create Compone  | nt Instance 🛛 🔀                                  |

|-----------------|--------------------------------------------------|

| Owning Project: | C:\Examples\Verilog\PCI_Advanced\PCI.hpj         |

| Instance of:    | c:\Examples\Verilog\PCI_Advanced\slave\slave.hpj |

| Instance Name:  | slave1                                           |

|                 | <u>D</u> K <u>C</u> ancel                        |

- Click OK to close the dialog and add the component instance (green chip icon) to Component Model folder.

After the component instance is created, the port mappings should be edited in order to hook up the model to the signals in the owning project, unless the default port mapping are correct. To edit the port mapping for a component instance:

- In the **Component Model** folder, double-click on the name of the component instance to open the *Component Instance Signals and Ports* dialog.

- The top part of the dialog displays the ports of the sub-component. The **Port Mapping** column are the signal names that will be mapped to the sub-components outputs.

- To change the port mapping, double-click on a cell in the **Port Mapping** column and either type in a name or choose a signal name from the drop-down list. The signals in the list are the signals in the current project or the ports of the MUT.

- Click **OK** to apply the port mapping and close the dialog.

For more information about the Component Signals and Ports dialog, see Section 2.6: Signals and Ports for Components.

The Component Instance will be added to the *Project* window under the Component Model of the owning project. A green chip icon is used in the project tree to represent a Component Instance. If the Project Component that is instantiated by the Component Instance has ports, then the port mapping will appear beside the Component Instance.

# 2.5 Component and Component Instance Generation Properties

The top-level component of the project and each instance of a sub-project has its own set of properties that determine the way the code is generated for the component. These properties are edited through the *Project Generation Properties* dialog. This dialog also gives you access to the variables, parameters, and signal mappings of the Component. To open the *Project Generation Properties* dialog:

Right-click on either the Component Model folder or on a component instance and choose Project Generation Properties or Component Instance Generation Properties from the drop-down list box to open the Project Generation Properties dialog.

The controls in this dialog change depending on if you are editing a Component Instance or the actual Component Model. For a Component Instance the following properties can be set:

- The **Instance Name** box indicates which component instance is being edited and allows you can change the name of the component instance.

- Checking the Edit All Instances check box indicates that changes in the properties will affect all instances of a

project. If you are editing from the Component Model folder of either the containing project or in a subprojects Component Model folder you will be editing all of the instances.

- The **Signals and Ports** button opens a dialog that lets you edit how the component instance is hooked up to the containing project.

- The **Class Methods** button opens a dialog that lets you edit the project level class methods (transaction level class methods must be edited from the transaction). See *Section 8.7: Class Methods* for more information.

| stance Name:<br>plave0       | Language:<br>Verilog             | ОК     |

|------------------------------|----------------------------------|--------|

| Edit All Instances           | Enable TestBuilder Integration   | Cancel |

| Enable Reference Model       |                                  | Apply  |

| Enable Transaction Manager   | 🔲 Generate Test Top              |        |

| Add Timestamp to Each File   | Verbose Transaction Logging      |        |

| Source Indent Size: 2        | Transaction Recording (Database) |        |

| Prefix Generated Files With: |                                  |        |

The top-level project and each sub-project definition contain defaults for the component generation properties used during code generation. The properties for this component can be edited by finding the **Component Model** folder and then opening the *Project Generation Properties* dialog. For sub-projects, the **Component Model** folder is located under the **Project Library** folder tree. When you are editing the properties at the component level you are editing all instances of that component. The following properties can be edited at the Component Model level:

- Enable Reference Model enables the generation of a golden reference model in C++, VHDL or Verilog. This feature is covered in *Section 2.7: Golden Reference Models*.

- Enable Transaction Manager enables the generation of the transaction manager code. This feature is covered in *Section 9.3: Transaction Manager and Test Reader*.

| Project Generation Properties fo | or slave                            | ×      |

|----------------------------------|-------------------------------------|--------|

| Component Module Name:<br>slave  | Language:<br>Verilog                | ОК     |

| 🔽 Edit All Instances             | 🔲 Enable TestBuilder Integration    | Cancel |

| 🔲 Enable Reference Model         |                                     | Apply  |

| 🔲 Enable Transaction Manager     | 🔲 Generate Test Top                 |        |

| 🔽 Add Timestamp to Each File     | Verbose Transaction Logging         |        |

| Source Indent Size: 2            | 🗖 Transaction Recording (Database)  |        |

| Prefix Generated Files With:     |                                     |        |

|                                  |                                     |        |

| Signals and Ports                | Classes and Variables Class Method: | 5      |

- Language and Enable TestBuilder control the generation language for this component. If the language for the project is changed, then the project template file must also be changed. *Section 9.6: Changing a Project Template File* discusses changing the project template file.

- The Generate Test Top checkbox is currently not in use.

- Add Timestamp to Each File is useful when the generated code is versioned. Disabling this will prevent the generated file from being different just because the time is different.

- Verbose Transaction Logging turns on extra reporting features for the Component Model and its transactions. This is useful for debugging and testing your components.

- The **Source Indent Size** specifies the number of spaces that are used for indenting blocks of code.

- Transaction Recording enables SDI transaction recording calls. These record every transaction that is run during simulation along with applied parameters. This is written to a database that can then be imported into Cadence's SignalScan. The simulation can then be viewed as a set of transactions.

- The **Prefix Generated Files With** edit box allows a line of text to be output at the beginning of each generated file. This is useful for noting author information or for adding keywords for version systems.

- The **Signals and Ports** button opens a dialog used to specify which signals will be available to external projects. It also allows you to define internal signals that are not contained in any transaction diagram.

- The **Classes and Variables** button opens a dialog that is used to edit the classes and variables that are included in that project. See *Chapter 8: Classes and Variables* for more information.

- The **Class Methods** button opens a dialog that lets you edit the project level class methods (transaction level class methods must be edited from the transaction). See *Section 8.7: Class Methods* for more information.

### 2.6 Signals and Ports for Components

The *Signals and Ports* dialog is used to view and edit the ports and internal signals of Component Models and definitions as well as the port mappings of Component Instances. TestBencher automatically creates certain signal and port information based on the Model Under Test and diagram ports. Internal signals are also created automatically based on the specified port mappings for component instances.

To open the Signals and Ports dialog:

- Right click the item to be edited (a Component Model, Component Definition or a Component Instance) and select **Signals and Ports** from the context menu. This will open the *Signals and Ports* dialog.

- Note: This dialog is modal, which means that selecting any Component or Component Instance in the *Project* window will update the information displayed in the dialog for the selected item.

Editing signals and ports with the dialog:

- The signals and ports that have gray cells are automatically generated for the MUT and diagram ports, as well as from port mappings that have been defined from child projects.

- For Component Definitions, internal signals can have their direction edited, and ports can have either the direction, default port mapping, or the initial value edited.

| Comp | omponent Model Signals and Ports for: slave |            |           |           |           |              |               |  |  |

|------|---------------------------------------------|------------|-----------|-----------|-----------|--------------|---------------|--|--|

| Con  | nponent Ports                               | ; (exporte | d signal: | s):       |           |              |               |  |  |

|      | Signals                                     | Msb        | Lsb       | Data Type | Direction | Default Port | Initial Value |  |  |

| 0    | CLK                                         | 0          | 0         | 4_state   | input     | CLK          |               |  |  |

| 1    | FRAMEn                                      | 0          | 0         | 4_state   | input     | FRAMEn       |               |  |  |

| 2    | AD                                          | 31         | 0         | 4_state   | inout     | AD           | 'hAE          |  |  |

| 3    | CBED                                        | 3          | 0         | 4 state   | input     | CBEn         |               |  |  |

- Component Instance internal signals can not be edited, and ports can have only the specific Port Mapping for the instance modified.

| Component Instance Signals and Ports for: PCI_slave0 |               |            |           |           |           |              |               |

|------------------------------------------------------|---------------|------------|-----------|-----------|-----------|--------------|---------------|

| Co                                                   | mponent Ports | ; (exporte | d signal: | s):       |           |              |               |

|                                                      | Signals       | Msb        | Lsb       | Data Type | Direction | Port Mapping | Initial Value |

| 0                                                    | CLK           | 0          | 0         | 4_state   | input     | CLK          |               |

| 1                                                    | FRAMEn        | 0          | 0         | 4_state   | input     | FRAMEn       |               |

| 2                                                    | AD            | 31         | 0         | 4_state   | inout     | AD[63:32]    | 'hAE          |

| 3                                                    | CBEn          | 3          | 0         | 4 state   | input     | CBEn         |               |

- New component level signals can be added when editing signals and ports for the Component Model (the component definition) by clicking the New Signal button. These signals can be made ports by changing the Direction of the signal from internal to input or output, or by dragging and dropping the signal from the bottom grid tree to the top. Note that when editing a Component Instance the signal and port definitions can not be changed.

- Port Mappings can be specified by double clicking a cell in the Default Port Mapping or Port Mapping column. When working with a Component Definition, the Default Port Mapping specified provides a default that will be used for the instances of the component being edited. If a Component Instance is being edited then the actual Port Mapping for that instance is being specified.

- If the signal that the port should connect to is not yet defined in the owning component, just type the name of the new signal into the **Port Mapping** column. TestBencher will automatically create a new signal in the owning component for this connection.

- A bit slice can be specified for each Port Mapping. TestBencher allows a bit slice to be specified as part of the port mapping, so that the connecting signal may be larger than the port. If the specified bit slice for the port mapping is outside of the connecting signal's bit range in the owning component, TestBencher will automatically combine the two bit slices in the connecting signal. Each time the test bench is generated the bit ranges of component signals will be verified. This means that if a bit range is extended, but then no longer needed it will be reduced to its original size. The only case in which this will not happen is if the signal was explicitly added in the Signals and Ports dialog by the user. In this case, TestBencher may need to extend the bit range, but will never reduce it. The Component Instance Signals and Ports image above shows an example of a bit slice specification for port AD.

- The Initial Value column provided for ports when editing a Component Definition allows an initialization for the port to be provided. The string entered in this field is placed directly into the generated source code without formatting. This value can not be edited at the Component Instance level. The images above show an example of specifying an initial value for port AD.

The Component Model has both exported signals and internal signals. By default, all signals that are generated by Test-Bencher are internal, but the Component Signals and Ports dialog allows these signals to be exported by simply changing the direction of the signal.

# 2.7 Golden Reference Models

TestBencher can generate C++, VHDL and Verilog golden reference models that run in parallel with a VHDL or Verilog RTL model. Golden reference models are high-level descriptions of a design and are used to compare to the results of an RTL-level model during simulation. Reference models usually model interaction between components at the transaction level (e.g. read transaction/write transaction) instead of at the signal level. When the reference model is created the apply calls will call both the diagram transactions and the equvalent reference model transaction. At the end of each transaction the outputs for the MUT and the reference model are compared and logged to the simulation log file.

# **Golden Reference Model**

TestBencher generates all of the stub-functions for the golden reference model, keeping the transaction interface to the reference model the same as the HDL level model. TestBencher uses the TestBuilder library to generate the C++ models. The user writes the behavioral C++, VHDL or Verilog code inside the stub-functions that enables the golden reference model to emulate the RTL-level model. To enable Reference Model Generation:

- In the *Project* window, right click on the **Component Model** folder and choose **Project Generation Properties** from the context menu. This opens the *Project Generation Properties* dialog.

- Check the Enable Reference Model checkbox and click OK to close the dialog.

- During the next code generation TestBencher will generate either a C++ or Verilog reference module depending on the generation language. *Section 10.1:Generate the Bus Functional Model* describes how to generate the project code.

- The reference model file is written to the Project directory and is named *projectName\_skeleton* with the appropriate extension for the language (.cpp, .vhd, or .v). For C++ there is also a header file named *projectName\_emulator.h* that contains the cless declaration for the reference model.

- Copy the projectName\_skeleton.cpp, .vhd or .v to a file named projectName\_emulator.cpp, .vhd or .v.

- Inside *projectName\_*emulator file uncomment any functions that you want to model, and insert behavioral code into the functions.

- Section 10.2: Simulator and Compiler Settings Dialog describes how to setup the C++ compiler so the Test-Bencher can compile the model and hand it off to the HDL simulator.

- During the simulation the reference model will automatically compare the results of the MUT to the results of the reference model and send the results to the simulation log file.

#### 2.8 Libraries and Use Clauses (VHDL only)

The *VHDL Libraries and Use Clauses to Include* dialog allows you to control the libraries and use clauses used by the VHDL diagrams in your project and by the top-level template file of the project.

To open the VHDL Libraries and Use Clauses dialog:

- Select Options > VHDL Libraries and Use Clauses... from the main menu.

OR

- Right-click on the project and choose VHDL Libraries and Use Clauses... from the context menu.

Changes made in this dialog will be applied to the current project, and stored in the **.hpj** file. If no project is open then the current settings will be applied to any new projects that are created, and saved in the TestBencher configuration.

The **View** dropdown allows you to change between selecting the VHDL libraries and the use clauses to include in your diagram.

#### To edit or add a new use clause or library include:

- Select Use Clauses or VHDL Libraries from the View dropdown.

- Double-click on an entry or on the first

| VHDL Libraries and Use Clauses to Include 📃 🔲 🗙                 |

|-----------------------------------------------------------------|

| View: Use Clauses                                               |

| Use Clauses                                                     |

| use myLib1.all;                                                 |

| myLib2.all;                                                     |

| myLib3.all                                                      |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

| <u>OK</u> <u>Cancel</u> <u>Save Defaults</u> <u>Delete Item</u> |

|                                                                 |

empty line in the list window and type in the use clause or library name. If the *use* or *library* tag is omitted from the statement, TestBencher will automatically add the tag to the statement before including it in the source code. Semicolons are also added as needed.

- All three of the following use clauses will work:

```

use myLib1.all;

myLib2.all;

myLib3.all

```

- All three of the following VHDL Library statements will work:

```

library myLib1;

myLib2;

myLib3

```

#### To delete a use clause or library include:

- Click on a clause or library in the list window to select the entry.

- Click the Delete Item button.

The **OK** button saves the current settings and closes the dialog. The **Cancel** button closes the dialog without saving the new settings. The **Save Defaults** button allows the current settings to be applied to any new projects that are started. If no project is open then this button will not be present, as settings will automatically be saved as defaults.

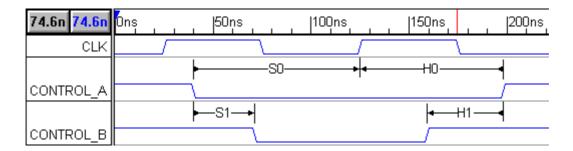

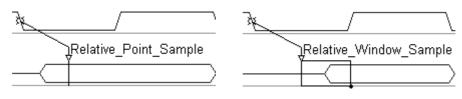

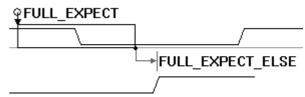

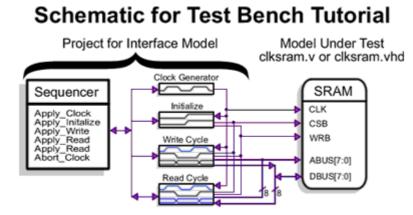

#### Exporting a diagram to VHDL