# Appendix C

# Peripheral Programming for Digital Signal Processors

This appendix introduces the details involved in interfacing the peripherals described in Chapter 3 with DSP processors. We discuss some important issues in the interfacing of peripherals, which include peripheral configuration, address connections of peripheral devices with DSP processors, and steps and coding involved to initialize peripheral devices. In this appendix, we use the Texas Instruments TMS320C5402 DSK as an example in explaining the interface between the DSP processor and peripheral devices.

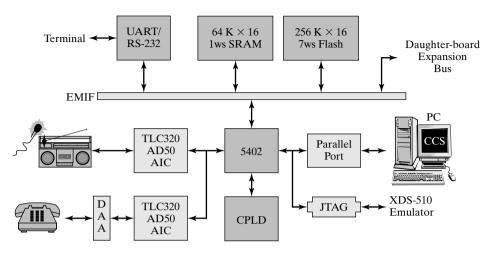

In the block diagram of the C5402 DSK, shown in Fig. C.1, the C5402 DSP is interfaced to the following peripheral devices:

- 1. Microphones/loudspeakers via TLC320AD50 analog interface circuits (AICs)

- 2. A host personal computer via a parallel port

- 3. An XDS-510 emulator via a JTAG port

- **4.** External memories and universal asynchronous receiver/transmitter (UART) via an EMIF

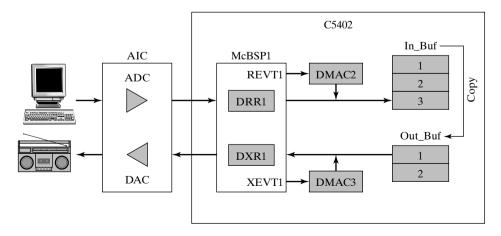

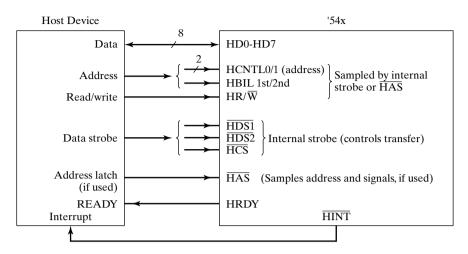

The C5402 DSP processor offers 16K words of on-chip memory, up to 100 MIPS, two McBSPs, one enhanced 8-bit HPI, and EMIFs to 64K static RAM, 256K flash, a

Figure C.1 Block diagram of the TMS320C5402 DSK (reprinted with permission from [1])

UART, and daughter boards. The following sections provide details regarding the CODEC and HPI interfacing on the C5402 DSK.

# C.1 INTERFACING WITH THE ANALOG INTERFACE CIRCUIT OR CODER-DECODER VIA DIRECT MEMORY ACCESS

As explained in Chapter 3, DMA and McBSP peripherals provide the mechanism for transferring data in and out of the DSP processor without the intervention of the processor. DMA allows movement of data to and from internal memory, internal peripherals, or external devices in the background of CPU operation. A general explanation of DMA/McBSP was given in Section 3.6.3, and more details are provided in this section.

#### C.1.1 Initializing a Multichannel Buffered Serial Port

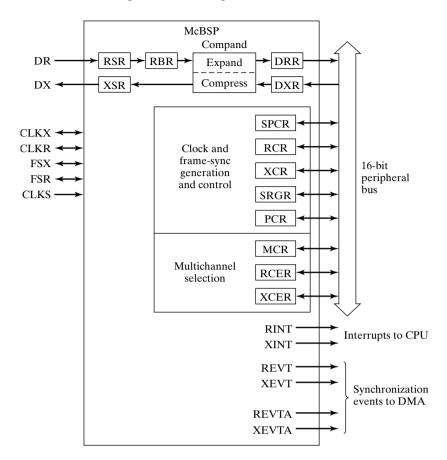

As shown in Fig. C.2, the McBSP provides a full-duplex direct interface to the AIC, the CODEC, and other serial devices. It supports a bit rate of up to half of the CPU clock rate, and it is able to support 8-, 12-, 16-, 20-, 24-, and 32-bit wordlengths. The two McBSPs used in the C5402 processor support up to 128 channels and have internal A-law and  $\mu$ -law companding circuits. The McBSP also includes independent framing and clocking for receiving and transmitting. Note that the McBSP has double-buffered transmit data registers (XSR and DXR) and triple-buffered receive data registers (RSR, RBR, and DRR).

As shown in Fig. C.2, the McBSP provides several interfacing pins for a group of clocking and frame-synchronization signals: (1) receive serial data (DR), (2) transmit serial data (DX), (3) transmit clock (CLKX), (4) receive clock (CLKR), (5) transmit frame synchronization (FSX), (6) receive frame synchronization (FSR), and (7) external clock (CLKS).

**Figure C.2** Block diagram of a McBSP and its interfacing pins (reprinted with permission from [2])

A group of signals in the McBSP is used to provide receive and transmit interrupts (RINT and XINT) to the CPU. Another group that provides event synchronization to the DMA contains (1) receive synchronization event (REVT), (2) transmit synchronization event (XEVT), (3) receive synchronization event A (REVTA), and (4) transmit synchronization event A (XEVTA).

As illustrated in Fig. C.2, serial data from external devices such as a CODEC are received at the DR pin of the McBSP and are shifted into the receive shift register (RSR) before being copied to the receive buffer register (RBR). The data in RBR is then moved to the data receive register (DRR) for a read by either the processor or the DMA controller. Data to be transmitted to an external device is written to the data transmit register (DXR), copied to the transmit shift register (XSR), and shifted out to the DX pin from XSR. Note that there are two sets of these registers, and the second set of registers (RSR2, RBR2, DRR2, DXR2, and XSR2) is not used if the transmit- or receive-data wordlength is 8, 12, or 16 bits.

# Appendix C Peripheral Programming for Digital Signal Processors

| Bit   | Name     | Function                           |                                                                                                                                                                                                                                                   |  |

|-------|----------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 15–14 | Reserved | Reserved                           |                                                                                                                                                                                                                                                   |  |

| 13    | XIOEN    | Transmit general                   | purpose I/O mode only when $\overline{\text{XRST}} = 0$ in SPCR                                                                                                                                                                                   |  |

|       |          | XIOEN = 0                          | DX, FSX and CLKX are configured as serial port pins<br>and do not function as general-purpose I/Os.                                                                                                                                               |  |

|       |          | XIOEN = 1                          | DX pin is a general purpose output. FSX and CLKX<br>are general purpose I/Os. These serial port pins do<br>not perform serial port operation.                                                                                                     |  |

| 12    | RIOEN    | Receive general p                  | purpose I/O mode only when $\overline{RRST} = 0$ in SPCR                                                                                                                                                                                          |  |

|       |          | RIOEN = 0                          | DR, FSR, CLKR and CLKS are configured as serial port pins and do not function as general-purpose I/Os.                                                                                                                                            |  |

|       |          | RIOEN = 1                          | DR and CLKS pins are general purpose inputs: FSR<br>and CLKR are general purpose I/Os. These serial<br>port pins do not perform serial port operation. The<br>CLKS pin is affected by a combination of RRST and<br>RIOEN signals of the receiver. |  |

| 11    | FSXM     | Transmit Frame-S                   | Synchronization Mode                                                                                                                                                                                                                              |  |

|       |          | FSXM = 0                           | Frame-synchronization signal derived from an external source                                                                                                                                                                                      |  |

|       |          | FSXM = 1                           | Frame synchronization is determined by the sample<br>rate generator frame-synchronization mode bit<br>FSGM in SRGR2.                                                                                                                              |  |

| 10    | FSRM     | Receive Frame-Synchronization Mode |                                                                                                                                                                                                                                                   |  |

|       |          | FSRM = 0                           | Frame-synchronization pulses generated by an external device. FSR is an input pin                                                                                                                                                                 |  |

|       |          | FSRM = 1                           | Frame synchronization generated internally by sample<br>rate generator. FSR is an output pin except when<br>GSYNC = 1 in SRGR.                                                                                                                    |  |

| 9     | CLKXM    | Transmitter Clock                  | k Mode                                                                                                                                                                                                                                            |  |

|       |          | CLKXM = 0                          | Transmitter clock is driven by an external clock with CLKX as an input pin.                                                                                                                                                                       |  |

|       |          | CLKXM = 1                          | CLKX is an output pin and is driven by the internal sample rate generator.                                                                                                                                                                        |  |

|       |          | During SPI mode                    | e (when CLKSTP is a non-zero value):                                                                                                                                                                                                              |  |

|       |          | CLKXM = 0                          | McBSP is a slave and clock (CLKX) is driven by the<br>SPI master in the system CLKR is internally driven<br>by CLKX.                                                                                                                              |  |

|       |          | CLKXM = 1                          | McBSP is a master and generates the clock (CLKX) to<br>drive its receive clock (CLKR) and the shift clock of<br>the SPI-compliant slaves in the system.                                                                                           |  |

**TABLE C.1** Description of the Pin Control Register (PCR) (reprinted with permission from [2])

C4

(Continued)

# TABLE C.1 (Continued)

| Bit | Name      | Function                                                                                     |                                                                                                                                                         |

|-----|-----------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   | CLKRM     | Receiver Clock Mode                                                                          |                                                                                                                                                         |

|     |           | Case 1: Digital loop back mode not set $(DLB = 0)$ in SPCR1                                  |                                                                                                                                                         |

|     |           | CLKRM = 0                                                                                    | Receive clock (CLKR) is an input driven by an external clock.                                                                                           |

|     |           | CLKRM = 1                                                                                    | CLKR is an output pin and is driven by the internal sample rate generator.                                                                              |

|     |           | Case 2: Digital lo                                                                           | op back mode set $(DLB = 1)$ in SPCR1                                                                                                                   |

|     |           | CLKRM = 0                                                                                    | Receive clock (not the CLKR pin) is driven by<br>transmit clock (CLKX) which is based on the<br>CLKXM bit in the PCR. CLKR pin is in<br>high-impedance. |

|     |           | CLKRM = 1                                                                                    | CLKR is an output pin and is driven by the transmit clock. The transmit clock is derived based on the CLKXM bit in the the PCR.                         |

| 7   | rsvd      | Reseved                                                                                      |                                                                                                                                                         |

| 6   | CLKS_STAT | CLKS pin status. Reflects value on CLKS pin when selected as a general purpose input.        |                                                                                                                                                         |

| 5   | DX_STAT   | DX pin status. Reflects value driven on to DX pin when selected as a general purpose output. |                                                                                                                                                         |

| 4   | DR_STAT   | DR pin status. Reflects value on DR pin when selected as a general purpose input.            |                                                                                                                                                         |

| 3   | FSXP      | Transmit Frame-Synchronization Polarity                                                      |                                                                                                                                                         |

|     |           | FSXP = 0                                                                                     | Frame-synchronization pulse FSX is active high                                                                                                          |

|     |           | FSXP = 1                                                                                     | Frame-synchronization pulse FSX is active low                                                                                                           |

| 2   | FSRP      | Receive Frame-S                                                                              | ynchronization Polarity                                                                                                                                 |

|     |           | FSRP = 0                                                                                     | Frame-synchronization pulse FSR is active high                                                                                                          |

|     |           | FSRP = 1                                                                                     | Frame-synchronization pulse FSR is active low                                                                                                           |

| 1   | CLKXP     | Transmit Clock Polarity                                                                      |                                                                                                                                                         |

|     |           | CLKXP = 0                                                                                    | Transmit data sampled on rising edge of CLKX                                                                                                            |

|     |           | CLKXP = 1                                                                                    | Transmit data sampled on falling edge of CLKX                                                                                                           |

| 0   | CLKRP     | Receive Clock Po                                                                             | blarity                                                                                                                                                 |

|     |           | CLKRP = 0                                                                                    | Receive data sampled on falling edge of CLKR                                                                                                            |

|     |           | CLKRP = 1                                                                                    | Receive data sampled on rising edge of CLKR                                                                                                             |

In addition to the data registers, there are 15 control registers that configure the operating modes of the McBSP. The McBSP can be configured during the reset state. Detailed definitions and usages of McBSP control registers can be found in [2]. In this section, we briefly describe the functionalities of the following registers:

- McBSP pin control registers

- Serial port control registers

- · Transmit control registers and receive control registers

- Multichannel control registers

- Receive channel enable registers and transmit channel enable registers

- Sample rate generator registers

The pin control register (PCR) controls the following modes: (1) configure DX, FSX, and CLKX as general-purpose or serial-port pins; (2) configure DR, FSR, CLKR and CLKS as general-purpose or serial-port pins; (3) transmit frame synchronization derived from an external source or a sample rate generator; (4) receive frame synchronization generated by an external device or a sample rate generator; (5) transmit clock by external clock with CLKX as the input pin or by a sample rate generator with CLKX as the output pin; (6) receive clock by external clock with CLKR as the input pin or by a sample rate generator with CLKR as the input pin; (7) transmit frame-sync (active high or low) and clock polarity (rising edge or falling edge of CLKR). Detailed definitions of the PCR are summarized in Table C.1.

Serial port control register 1 (SPCR1) contains the McBSP receiver-status bits and the main switch to enable or disable the receiver. This register also includes the clock-stop mode bit and receiver-interrupt mode bits. Serial port control register 2 (SPCR2) contains the McBSP transmitter-status bits and the main switch to enable or disable the transmitter. This register also includes the bits to reset the frame-sync generator and the sample-rate generator. Functions of the SPCR1 and SPCR2 are summarized in Tables C.2 and C.3, respectively.

Transmit control registers 1 and 2 (XCR1 and XCR2) configure various parameters of transmit operations, including (1) transmit frame length (from 1 to 128 words per frame), (2) transmit wordlength (for 8, 12, 16, 20, 24, or 32 bits), (3) transmit frame (single or dual phase), (4) transmit companding (none,  $\mu$ -law, or A-law), (5) transmit frame synchronization, and (6) transmit data delay (0-, 1-, or 2-bit data delay). Tables C.4 and C.5 summarize the XCR1 and XCR2 bit-field descriptions, respectively.

Receive control registers 1 and 2 (RCR1 and RCR2) configure various parameters of receive operations, including (1) receive frame length (from 1 to 128 words per frame), (2) receive wordlength (for 8, 12, 16, 20, 24, or 32 bits), (3) receive frame (single or dual phase), (4) receive companding (none,  $\mu$ -law, or A-law), (5) receive frame synchronization, and (6) receive data delay (0-, 1-, or 2-bit data delay). Bitfield descriptions similar to those shown in Tables C.4 and C.5 are also applied to RCR1 and RCR2.

| Bit   | Name     | Function                               |                                                                             |  |

|-------|----------|----------------------------------------|-----------------------------------------------------------------------------|--|

| 15    | DLB      | Digital Loop Back Mode                 |                                                                             |  |

|       |          | $\mathbf{DLB}=0$                       | Digital loop back mode disabled                                             |  |

|       |          | DLB = 1                                | Digital loop back mode enabled                                              |  |

| 14–13 | RJUST    | Receive Sign-Extension                 | and Justification Mode.                                                     |  |

|       |          | RJUST = 00                             | Right-justify and zero-fill MSBs in DRR                                     |  |

|       |          | RJUST = 01                             | Right-justify and sign-extend MSBs in DRR                                   |  |

|       |          | RJUST = 10                             | Left-justify and zero-fill LSBs in DRR                                      |  |

|       |          | RJUST = 11                             | Reserved                                                                    |  |

| 12–11 | CLKSTP   | Clock Stop Mode<br>CLKSTP = 0X         | Clock stop mode disabled. Normal clocking for non-SPI mode.                 |  |

|       |          | Various SPI modes when                 | n:                                                                          |  |

|       |          | CLKSTP = 10  and $CLKXP = 0$           | Clock starts with rising edge without delay                                 |  |

|       |          | CLKSTP = 10 and<br>CLKXP = 1           | Clock starts with falling edge without delay                                |  |

|       |          | $CLKSTP = 11 \text{ and} \\ CLKXP = 0$ | Clock starts with rising edge with delay                                    |  |

|       |          | CLKSTP = 11 and<br>CLKXP = 1           | Clock starts with falling edge with delay                                   |  |

| 10–8  | reserved | Reserved                               |                                                                             |  |

| 7     | DXENA    | DX Enabler                             |                                                                             |  |

|       |          | DXENA = 0                              | DX enabler is off                                                           |  |

|       |          | DXENA = 1                              | DX enabler is on                                                            |  |

| 6     | ABIS     | ABIS Mode                              |                                                                             |  |

|       |          | ABIS = 0                               | A-bis mode is disabled                                                      |  |

|       |          | ABIS = 1                               | A-bis mode is enabled                                                       |  |

| 5–4   | RINTM    | Receive Interrupt Mode                 |                                                                             |  |

|       |          | RINTM = 00                             | RINT driven by RRDY (i.e., end of word) and end of frame in A-bis mode.     |  |

|       |          | RINTM = 01                             | RINT generated by end-of-block or<br>end-of-frame in multichannel operation |  |

|       |          | RINTM = 10                             | RINT generated by a new frame synchronization                               |  |

|       |          | RINTM = 11                             | RINT generated by RSYNCERR                                                  |  |

TABLE C.2

Description of Serial Port Control Register 1 (SPCR1) (reprinted with permission from [2])

(Continued)

**C**8

| Bit | Name     | Function                                                                                                                                                                                                         |                                                                                                                     |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 3   | RSYNCERR | Receive Synchronizatio<br>RSYNCERR = 0<br>RSYNCERR = 1                                                                                                                                                           | n Error<br>No synchronization error<br>Synchronization error detected by McBSP.                                     |

| 2   | RFULL    | Receive Shift Register (<br>RFULL = 0<br>RFULL = 1                                                                                                                                                               | (RSR) Full<br>RBR is not in overrun condition<br>DRR is not read, RBR is full and<br>RSR is also full with new word |

| 1   | RRDY     | Receiver Ready<br>RRDY = 0<br>RRDY = 1                                                                                                                                                                           | Receiver is not ready.<br>Receiver is ready with data to be read from<br>DRR.                                       |

| 0   | RRST     | Receiver reset. This resets and enables the receiver. $\overline{\text{RRST}} = 0$ The serial port receiver is disabled and in<br>reset state. $\overline{\text{RRST}} = 1$ The serial port receiver is enabled. |                                                                                                                     |

| TABLE C.3 | Description of Seria | Port Control Register | 2 (SPCR2) (reprinted wit | permission from [2]) |

|-----------|----------------------|-----------------------|--------------------------|----------------------|

|           | 20000.000.000.000.00 |                       |                          |                      |

| Bit   | Name | Function                                                                                  |                                                                                                                                                                                                       |

|-------|------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-10 | rsvd | Reserved                                                                                  |                                                                                                                                                                                                       |

| 9     | FREE | U                                                                                         | node is disabled<br>node is enabled                                                                                                                                                                   |

| 8     | SOFT | Soft BitSOFT = 0SOFT mode isSOFT = 1SOFT mode is                                          |                                                                                                                                                                                                       |

| 7     | FRST | $\overline{FRST} = 1$ $FSG is not g$ $\overline{FRST} = 1$ $Frame-sync sig$ $number of C$ | nization logic is reset. Frame-sync signal<br>enerated by the sample-rate generator.<br>nal FSG is generated after (FPER + 1)<br>LKG clocks; i.e., all frame counters are<br>their programmed values. |

| 6     | GRST | Sample-Rate Generator Reset $\overline{\text{GRST}} = 0$ Sample rate get                  | nerator is reset                                                                                                                                                                                      |

# Appen

(Continued)

| TABLE C.3 | (Continued) |

|-----------|-------------|

|-----------|-------------|

| Bit | Name     | Function                       |                                                                                                                                       |

|-----|----------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

|     |          | $\overline{\text{GRST}} = 1$   | Sample rate generator is pulled out of reset.<br>CLKG is driven as per programmed value<br>in sample rate generator registers (SRGR). |

| 5–4 | XINTM    | Transmit Interrupt Mo          | de                                                                                                                                    |

|     |          | XINTM = 00                     | XINT driven by XRDY (i.e., end of word)<br>and end of frame in A-bis mode.                                                            |

|     |          | XINTM = 01                     | XINT generated by end-of-block or<br>end-of-frame in multichannel operation                                                           |

|     |          | XINTM = 10                     | XINT generated by a new frame synchronization                                                                                         |

|     |          | XINTM = 11                     | XINT generated by XSYNCERR                                                                                                            |

| 3   | XSYNCERR | Transmit Synchronizati         | on Error                                                                                                                              |

|     |          | XSYNCERR = 0                   | No synchronization error                                                                                                              |

|     |          | XSYNCERR = 1                   | Synchronization error detected by McBSP.                                                                                              |

| 2   | XEMPTY   | Transmit Shift Register        | (XSR) Empty                                                                                                                           |

|     |          | $\overline{\text{XEMPTY}} = 0$ | XSR is empty                                                                                                                          |

|     |          | $\overline{\text{XEMPTY}} = 1$ | XSR is not empty                                                                                                                      |

| 1   | XRDY     | Transmitter Ready              |                                                                                                                                       |

|     |          | XRDY = 0                       | Transmitter is not ready.                                                                                                             |

|     |          | XRDY = 1                       | Transmitter is ready for new data in DXR.                                                                                             |

| 0   | XRST     | Transmitter Reset              | This resets and enables the transmitter.                                                                                              |

|     |          | $\overline{\text{XRST}} = 0$   | The serial port transmitter is disabled and in reset state.                                                                           |

|     |          | $\overline{\text{XRST}} = 1$   | The serial port transmitter is enabled.                                                                                               |

Multichannel registers 1 and 2 (MCR1 and MCR2) independently select the channels to be used. These registers select the following options: (1) receive and transmit partition A block (each mode selects all-odd blocks of 16 channels), (2) receive and transmit partition B block (each mode selects all-even blocks of 16 channels), (3) receive and transmit current block (each mode selects 1 of the 8 possible blocks), and (4) receive and transmit multichannel selection enable (selects either all 128 channels or select 1 of the 8 blocks, which is enabled by receive partition block registers). Table C.6 shows MCR1 configured as the receiver, while Table C.7 shows MCR2 configured as the transmitter.

Receive channel enable register partition A (RCERA) and B (RCERB) are used to enable any of 32 channels for receive. Out of the 32 channels, 16 channels belong to a block in partition A, and the other 16 belong to a block in partition B. The 16-bit RCERA enables or disables each channel in an even-numbered block

**TABLE C.4** Partial Bit-Field Description of Transmit Control Register 1 (XCR1)

(reprinted with permission from [2])

C10

| Bit  | Name    | Function                                                                                                                                      |                                                                           |

|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 15   | rsvd    | Reserved                                                                                                                                      |                                                                           |

| 14–8 | XFRLEN1 | Transmit Frame Length 1<br>XFRLEN1 = 000 0000<br>XFRLEN1 = 000 0001                                                                           | 1 word per frame<br>2 words per frame                                     |

|      |         | RFRLEN1 = 111 1111                                                                                                                            | 128 words per frame                                                       |

| 7–5  | XWDLEN1 | Transmit Word Length 1<br>XWDLEN1 = 000<br>XWDLEN1 = 001<br>XWDLEN1 = 010<br>XWDLEN1 = 011<br>XWDLEN1 = 100<br>XWDLEN1 = 101<br>XWDLEN1 = 11X | 8 bits<br>12 bits<br>16 bits<br>20 bits<br>24 bits<br>32 bits<br>Reserved |

| 4-0  | rsvd    | Reserved                                                                                                                                      |                                                                           |

**TABLE C.5** Bit-Field Description of Transmit Control Register 2 (XCR2) (reprinted with permission from [2])

| Bit  | Name    | Function                                                                                  |                                                     |

|------|---------|-------------------------------------------------------------------------------------------|-----------------------------------------------------|

| 15   | XPHASE  | Transmit Phases<br>XPHASE = 0<br>XPHASE = 1                                               | Single-phase frame<br>Dual-phase frame              |

| 14-8 | XFRLEN2 | Transmit Frame Length 2<br>XFRLEN2 = 000 0000<br>XFRLEN2 = 000 0001<br>XFRLEN1 = 111 1111 | 1 word per frame<br>2 words per frame<br> <br>      |

| 7–5  | XWDLEN2 | Transmit Word Length 2<br>XWDLEN2 = 000<br>XWDLEN2 = 001<br>XWDLEN2 = 010                 | 128 words per frame<br>8 bits<br>12 bits<br>16 bits |

(*Continued*)

| Bit | Name     | Function                                                                                                                  |                                                                                        |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

|     |          | XWDLEN2 = 011                                                                                                             | 20 bits                                                                                |

|     |          | XWDLEN2 = 100                                                                                                             | 24 bits                                                                                |

|     |          | XWDLEN2 = 101                                                                                                             | 32 bits                                                                                |

|     |          | XWDLEN2 = 11X                                                                                                             | Reserved                                                                               |

| 4–3 | XCOMPAND | Transmit companding mode. Modes other than 00b are o<br>enabled when the appropriate XWDLEN is 000b, indic<br>8-bit data. |                                                                                        |

|     |          | XCOMPAND = 00                                                                                                             | No companding, data<br>transfer starts with MSB<br>first.                              |

|     |          | XCOMPAND = 01                                                                                                             | No companding, 8-bit data,<br>transfer starts with LSB<br>first.                       |

|     |          | XCOMPAND = 10                                                                                                             | Compand using $\mu$ -law for transmit data.                                            |

|     |          | XCOMPAND = 11                                                                                                             | Compand using A-law for transmit data.                                                 |

| 2   | XFIG     | Transmit Frame Ignore                                                                                                     |                                                                                        |

|     |          | XFIG = 0                                                                                                                  | Transmit frame-<br>synchronization pulses<br>after the first restarts the<br>transfer. |

|     |          | XFIG = 1                                                                                                                  | Transmit frame-<br>synchronization pulses<br>after the first are ignored.              |

| 1-0 | XDATDLY  | Transmit Data Delay                                                                                                       |                                                                                        |

|     |          | XDATDLY = 00                                                                                                              | 0-bit data delay                                                                       |

|     |          | XDATDLY = 01                                                                                                              | 1-bit data delay                                                                       |

|     |          | XDATDLY = 10                                                                                                              | 2-bit data delay                                                                       |

|     |          | XDATDLY = 11                                                                                                              | Reserved                                                                               |

in partition A, while RCERB enables or disables each channel in an odd-numbered block in partition B. Table C.8 describes the RCERA and RCERB registers.

Transmit channel enable register partition A (XCERA) and B (XCERB) operate similarly to the receive channel enable registers, except that they are used to enable any of the 32 channels for transmission. The XCERA and XCERB registers use the same bit descriptions as those shown in Table C.8.

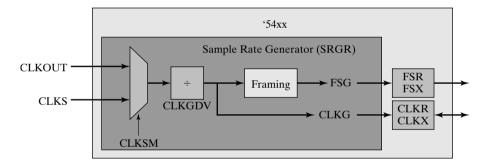

The sample rate generator (SRGR) is composed of a clock divider that generates a programmable data clock (CLKG) and a framing signal (FSG), as shown in Fig. C.3. These internal signals are then used to drive the receive and transmit clocks

| Bit  | Name   | Function                  |                                                                                                                               |  |

|------|--------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| 15–9 | rsvd   | Reserved                  |                                                                                                                               |  |

| 8–7  | RPBBLK | Receive Partition B Block |                                                                                                                               |  |

|      |        | RPBBLK = 00               | Block 1. Channel 16 to channel 31                                                                                             |  |

|      |        | RPBBLK = $01$             | Block 3. Channel 48 to channel 63                                                                                             |  |

|      |        | RPBBLK = 10               | Block 5. Channel 80 to channel 95                                                                                             |  |

|      |        | RPBBLK = $11$             | Block 7. Channel 112 to channel 127                                                                                           |  |

| 6–5  | RPABLK | Receive Partition A Blo   | ock                                                                                                                           |  |

|      |        | RPABLK = 00               | Block 0. Channel 0 to channel 15                                                                                              |  |

|      |        | RPABLK = 01               | Block 2. Channel 32 to channel 47                                                                                             |  |

|      |        | RPABLK = 10               | Block 4. Channel 64 to channel 79                                                                                             |  |

|      |        | RPABLK = 11               | Block 6. Channel 96 to channel 111                                                                                            |  |

| 4–2  | RCBLK  | Receive Current Block     |                                                                                                                               |  |

|      |        | RCBLK = 000               | Block 0. Channel 0 to channel 15                                                                                              |  |

|      |        | RCBLK = 001               | Block 1. Channel 16 to channel 31                                                                                             |  |

|      |        | RCBLK = 010               | Block 2. Channel 32 to channel 47                                                                                             |  |

|      |        | RCBLK = 011               | Block 3. Channel 48 to channel 63                                                                                             |  |

|      |        | RCBLK = 100               | Block 4. Channel 64 to channel 79                                                                                             |  |

|      |        | RCBLK = 101               | Block 5. Channel 80 to channel 95                                                                                             |  |

|      |        | RCBLK = 110               | Block 6. Channel 96 to channel 111                                                                                            |  |

|      |        | RCBLK = 111               | Block 7. Channel 112 to channel 127                                                                                           |  |

| 1    | rsvd   | Reserved                  |                                                                                                                               |  |

| 0    | RMCM   | Receive Multichannel S    | Selection Enable                                                                                                              |  |

|      |        | RMCM = 0                  | All 128 channels enabled.                                                                                                     |  |

|      |        | RMCM = 1                  | All channels disabled by default.<br>Required channels are selected by<br>enabling RP(A/B)BLK and<br>RCER(A/B) appropriately. |  |

TABLE C.6 Multichannel Control Register 1 (MCR1) (reprinted with permission from [2])

(CLKR/CLKX) and the receive/transmit framing signal (FSR/FSX). The sample rate generator can be programmed to divide either an internal-clock source or an internal clock derived from an external-clock source.

The sample rate generator registers SRGR1 and SRGR2 control the operations of the sample rate generator, including (1) frame width (FWID), which determines the width of the frame-sync pulse (1 to 256 CLKG periods); (2) sample rate generator clock divider (CLKGDV), which generates the required sample rate generator clock frequency (default = 1 and maximum = 255); (3) sample

C12

# Section C.1 Interfacing with the Analog Interface Circuit

| Bit        | Name   | Function               |                                                                                                                                                                                                                                                                                            |

|------------|--------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–9       | rsvd   | Reserved               |                                                                                                                                                                                                                                                                                            |

| 8–7 XPABLK |        | Transmit Partition A   | Block                                                                                                                                                                                                                                                                                      |

|            |        | XPABLK = 00            | Block 0. Channel 0 to channel 15                                                                                                                                                                                                                                                           |

|            |        | XPABLK = 01            | Block 2. Channel 32 to channel 47                                                                                                                                                                                                                                                          |

|            |        | XPABLK = 10            | Block 4. Channel 64 to channel 79                                                                                                                                                                                                                                                          |

|            |        | XPABLK = 11            | Block 6. Channel 96 to channel 111                                                                                                                                                                                                                                                         |

| 6–5        | XPBBLK | Transmit Partition E   | Block                                                                                                                                                                                                                                                                                      |

|            |        | XPBBLK = 00            | Block 1. Channel 16 to channel 31                                                                                                                                                                                                                                                          |

|            |        | XPBBLK = 01            | Block 3. Channel 48 to channel 63                                                                                                                                                                                                                                                          |

|            |        | XPBBLK = 10            | Block 5. Channel 80 to channel 95                                                                                                                                                                                                                                                          |

|            |        | XPBBLK = 11            | Block 7. Channel 112 to channel 127                                                                                                                                                                                                                                                        |

| 4–2        | XCBLK  | Transmit Current Bl    | lock                                                                                                                                                                                                                                                                                       |

|            |        | XCBLK = 000            | Block 0. Channel 0 to channel 15                                                                                                                                                                                                                                                           |

|            |        | XCBLK = 001            | Block 1. Channel 16 to channel 31                                                                                                                                                                                                                                                          |

|            |        | XCBLK = 010            | Block 2. Channel 32 to channel 47                                                                                                                                                                                                                                                          |

|            |        | $\mathbf{XCBLK} = 011$ | Block 3. Channel 48 to channel 63                                                                                                                                                                                                                                                          |

|            |        | XCBLK = 100            | Block 4. Channel 64 to channel 79                                                                                                                                                                                                                                                          |

|            |        | XCBLK = 101            | Block 5. Channel 80 to channel 95                                                                                                                                                                                                                                                          |

|            |        | XCBLK = 110            | Block 6. Channel 96 to channel 111                                                                                                                                                                                                                                                         |

|            |        | $\mathbf{XCBLK} = 111$ | Block 7. Channel 112 to channel 127                                                                                                                                                                                                                                                        |

| 1-0        | XMCM   | Transmit Multichani    | nel Selection Enable                                                                                                                                                                                                                                                                       |

|            |        | XMCM = 00              | All channels enabled without masking (DX is always driven during transmission of data <sup>†</sup> ).                                                                                                                                                                                      |

|            |        | XMCM = 01              | All channels disabled and therefore masked<br>by default. Required channels are selected<br>by enabling XP(A/B)BLK and XCER(A/B)<br>appropriately. Also, these selected channels<br>are not masked and therefore DX is always<br>driven.                                                   |

|            |        | XMCM = 10              | All channels enabled, but masked. Selected<br>channels enabled via XP(A/B)BLK and<br>XCER(A/B) are unmasked.                                                                                                                                                                               |

|            |        | XMCM = 11              | All channels disabled and therefore masked<br>by default. Required channels are selected<br>by enabling RP(A/B)BLK and RCER(A/B)<br>appropriately. Selected channels can be<br>unmasked by RP(A/B)BLK and<br>XCER(A/B). This mode is used for<br>symmetric transmit and receive operation. |

TABLE C.7

Multichannel Control Register 2 (MCR2) (reprinted with permission from [2])

**TABLE C.8** Receive Channel Enable Register Partitions A and B (RCERA) and (RCERB) (reprinted with permission from [2])

| Bit  | Name       | Function                                                                                        |  |

|------|------------|-------------------------------------------------------------------------------------------------|--|

| 15–0 | RCEA(0.15) | Receive Channel Enable-                                                                         |  |

|      |            | RCEA $n = 0$ Disables reception of <i>n</i> th channel in an even-numbered block in partition A |  |

|      |            | RCEA $n = 1$ Enables reception of <i>n</i> th channel in an even-numbered block in partition A  |  |

|      |            |                                                                                                 |  |

| Bit  | Name       | Function                                                                                        |                                                   |

|------|------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 15–0 | RCEB(0.15) | Receive Channel Enable-                                                                         |                                                   |

|      |            | RCEB $n = 0$ Disables reception of <i>n</i> th channel in an even-numbered block in partition B |                                                   |

|      |            | RCEB $n = 1$ Enables reception<br>even-numbered                                                 | of <i>n</i> th channel in an block in partition B |

Figure C.3 Internal blocks of the sample rate generator (reprinted with permission from [3])

rate generator clock synchronization (GSYNC); (4) CLKS polarity clock edge select (CLKSP); (5) McBSP sample rate generator clock (CLKSM); (6) sample rate generator transmit frame-synchronization (FSGM); and (7) frame period (FRER), which can be set from 1 to 4,096 CLKG periods. Tables C.9 and C.10 summarize the functions of the SRGR1 and SRGR2 registers, respectively.

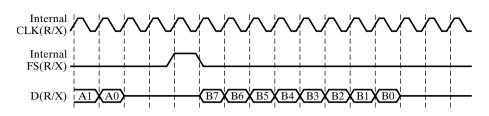

Having introduced the McBSP registers, we now examine how to configure clocking and framing signals using these registers. Figure C.4 shows the typical operations of the internal McBSP clock and frame-sync signals, as well as the data bits. The polarities (active high or low) of FSR, FSX, CLKX, and CLKR can be selected by the PCR register.

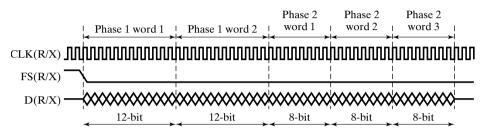

Figure C.5 shows an example of a dual-phase frame consisting of 2 words and 3 words in phases 1 and 2, respectively. The wordlength in phase 1 is 12 bits and in phase 2 is 8 bits. Using Tables C.4 and C.5, we can specify the preceding dual-phase

# Section C.1 Interfacing with the Analog Interface Circuit

| Bit  | Name   | Function                                                                                                                         |  |

|------|--------|----------------------------------------------------------------------------------------------------------------------------------|--|

| 15-8 | FWID   | Frame Width. This field plus 1 determines the width of the frame-syncpulse, FSG, during its active period.                       |  |

|      |        | Range: up to 2; 1 to 256 CLKG periods.                                                                                           |  |

| 7-0  | CLKGDV | Sample Rate Generator Clock Divider                                                                                              |  |

|      |        | This value is used as the divide-down number to generate the required sample rate generator clock frequency. Default value is 1. |  |

| TABLE C.9 | Sample Rate Contro | I Register 1 (SRGF | R1) (reprinted with p | permission from [2]) |

|-----------|--------------------|--------------------|-----------------------|----------------------|

|-----------|--------------------|--------------------|-----------------------|----------------------|

| TABLE C.10 | Sample Rate Control | Begister 2 (SRGR2)    | (reprinted with | permission from [2]) |

|------------|---------------------|-----------------------|-----------------|----------------------|

| IADEE 0.10 | oumple nate control | / nogistor 2 (ondit2) | (iopinitou with |                      |

| Bit  | Name  | Function                                                                                                                                                                                                                                                                                                                   |  |  |

|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 15   | GSYNC | <ul> <li>Sample Rate Generator Clock Synchronization</li> <li>Only used when the external clock (CLKS) drives the sample rate generator clock (CLKSM = 0).</li> <li>GSYNC = 0 The sample rate generator clock (CLKG) is free running.</li> <li>GSYNC = 1 The sample rate generator clock (CLKG) is running. But</li> </ul> |  |  |

|      |       | CLKG is resynchronized and frame-sync signal (FSG)<br>is generated only after detecting the receive<br>frame-synchronization signal (FSR). Also, frame period,<br>FPER, is a don't care because the period is dictated by<br>the external frame-sync pulse.                                                                |  |  |

| 14   | CLKSP | CLKS Polarity Clock Edge Select<br>Only used when the external clock CLKS drives the sample rate                                                                                                                                                                                                                           |  |  |

|      |       | generator clock (CLKSM = $0$ ).                                                                                                                                                                                                                                                                                            |  |  |

|      |       | CLKSP = 0 Rising edge of CLKS generates CLKG and FSG.                                                                                                                                                                                                                                                                      |  |  |

|      |       | CLKSP = 1 Falling edge of CLKS generates CLKG and FSG.                                                                                                                                                                                                                                                                     |  |  |

| 13   | CLKSM | McBSP Sample Rate Generator Clock Mode                                                                                                                                                                                                                                                                                     |  |  |

|      |       | CLKSM = 0Sample rate generator clock derived from the CLKS pin.CLKSM = 1Sample rate generator clock derived from CPU clock.                                                                                                                                                                                                |  |  |

| 12   | FSGM  | Sample Rate Generator Transmit Frame-Synchronization Mode Used<br>when FSXM = 1 in the PCR.                                                                                                                                                                                                                                |  |  |

|      |       | FSGM = 0 Transmit frame-sync signal (FSX) due to DXR<br>[1,2]-to-XSR[1,2] copy. When FSGM = 0, FPR and<br>FWID are ignored.                                                                                                                                                                                                |  |  |

|      |       | FSGM = 1 Transmit frame-sync signal driven by the sample rate generator frame-sync signal, FSG.                                                                                                                                                                                                                            |  |  |

| 11–0 | FPER  | Frame Period. This field plus 1 determines when the next frame-sync signal becomes active.                                                                                                                                                                                                                                 |  |  |

|      |       | Range: 1 to 4096 CLKG periods.                                                                                                                                                                                                                                                                                             |  |  |

Figure C.4 Typical operations of clock, frame-sync, and data signals (reprinted with permission from [2])

**Figure C.5** Dual-phase example with 12 bits per word and 2 words per phase in phase 1 and with 8 bits per word and 3 words per phase in phase 2 (reprinted with permission from [2])

frame in the following registers:

- X/RPHASE = 1, dual-phase frame

- X/RFRLEN1 = 000 0001, 2 words for phase 1

- X/RFRLEN2 = 000 0010, 3 words for phase 2

- X/RWDLEN1 = 001, 12 bits per word for phase 1

- X/RWDLEN2 = 000, 8 bits per word for phase 2

The maximum number of words per frame is 128 for a single-phase frame and 256 for a dual-phase frame. Altogether, the maximum number of bits per frame is  $128 \times 32 = 4,096$  for a single-phase frame and 8,192 for a dual-phase frame, assuming there are no gaps between words and frames. The frame frequency is determined by the period between frame-sync signals. Therefore, the maximum frame frequency is the bit-clock frequency divided by the number of bits per frame.

In addition, there are five serial-port events that may result in system error. They are summarized as follows:

- **1.** A receive overrun error occurs when DRR has not been read since the last data move from RBR to DRR.

- **2.** An unexpected receiver frame sync error happens when reset frame ignore (RFIG) = 0 and when an unexpected frame sync pulse occurs during reception.

- **3.** A transmit data overwrite error occurs when the user overwrites data in DXR before it has been copied to XSR.

- **4.** A transmit empty error occurs when a new frame sync signal arrives before the new data is loaded into the DXR. In this case, the old data in DXR is sent again.

- 5. An unexpected transmit frame sync error occurs when transmit frame ignore (XFIG) = 0 and when an unexpected frame sync pulse occurs during transmission.

In general, the following steps show how to transmit and receive data using the McBSP:

- **Step 1:** Reset the McBSP using either the device reset RS = 0, or independently reset serial-port transmit (XRST) = 0 and/or receiver reset (RRST) = 0.

- **Step 2:** Wait until the device reset is complete (RS = 1), then initialize the serial port using the following steps:

- **a.** Set XRST = RRST = frame-sync generator reset (FRST) = 0 in the SPCR1 and SPCR2 registers, which disables both the transmitter and the receiver and puts them in reset state.

- **b.** Program the McBSP configuration registers, including SPCR1, SPCR2, RCR1, RCR2, XCR1, XCR2, SPGR1, SPGR2, MCR1, MCR2, RCERA, RCERB, XCERA, XCERB, and PCR.

- c. Wait for a 2-bit clock period to ensure proper internal synchronization.

- d. Set up data acquisition such as writing to DXR.

- **e.** Enable the serial port by setting XRST = RRST = 1 in the SPCR1 and SPCR2 registers.

- **f.** Set FRST = 1 if an internal generated frame sync is required.

- **g.** Wait for a 2-bit clock period to ensure the receiver and transmitter become active.

- **Step 3:** Ensure the serial port has been initialized, and then determine whether the McBSP is ready by polling the receiver ready (RRDY) and transmitter ready (XRDY) signals, the DMA events (REVT and XEVT in normal mode), or the interrupts to CPU (RINT and XINT). In the case of the receiver, the condition RRDY = 1 indicates that the data in the RBR register have been copied to the DRR register, which implies that data can be read by the CPU or DMA. Once the data has been read, RRDY = 0. In the case of the transmitter, XRDY = 1 indicates that the DXR register contents have been copied to the XSR register. DXR is now ready to be loaded with a new data word. Once data is loaded, XRDY = 1.

#### C.1.2 Initializing Direct Memory Access

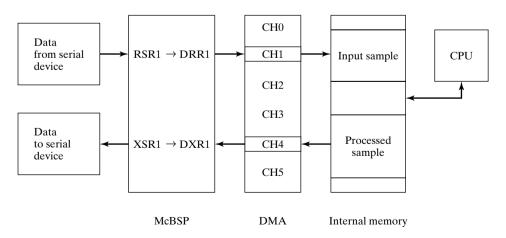

The DMA controller is used to transfer data between the McBSP and the internal memory of the processor without CPU intervention. For example, DMA can transfer

data from an external device to internal memory while the CPU is processing data located at another memory section, as shown in Fig. C.6. At the same time, a data sample from the processor can be sent out to an external device via another DMA channel. Six programmable DMA channels are available on the C54x processor. These channels allow six different DMA operations with programmable priorities. In addition to moving data between external peripherals and internal memory through the McBSP, DMA also allows data transfer between internal memory, internal peripherals, and HPI peripherals. The HPI interface is discussed in Section C.2.

There are several transfer operations in DMA:

C18

- **1.** A read transfer occurs when the DMA reads a data element from a source located in memory or from a peripheral device.

- **2.** A write transfer occurs when the DMA writes a data element during the preceding read transfer to the destination located in memory or to a peripheral device.

- **3.** An element transfer combines the preceding read and write transfers for a single data element.

- **4.** A frame transfer allows each of the six DMA channels in a C54x processor to program the number of elements per frame independently. A frame transfer is completed when the DMA moves all of the elements in a single frame.

- **5.** A block transfer allows each of the six DMA channels in a C54x processor to program the number of frames per block independently. A block transfer is completed when the DMA moves all of the frames defined in the block.

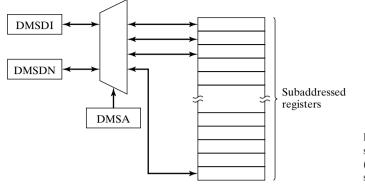

Similar to other peripherals, DMA must be configured before operation. The DMA controller has a group of memory-mapped registers that use a subaddressing scheme. Register subaddressing is a technique used in multiplexing a set of registers to a single location in the memory map. Therefore, a large set of registers can be mapped into a small memory space, as shown in Fig. C.7. It shows a subbank address

Figure C.6 DMA reading/writing data from/to a serial device to/from internal memory

**Figure C.7** Register subaddressing in DMA (reprinted with permission from [2])

register (DMSA), which directs the multiplexer to connect the subbank access registers (DMSDI and DMSDN) to the actual subaddressed registers. The difference between DMSDI and DMSDN is that DMSDI is incremented automatically after each access, while DMSDN is used for single-register access without modifying the subaddress.

Table C.11 lists the addresses, subaddresses, and functions of DMA registers. Only the first four registers listed in Table C.11 are directly addressed, while the rest of the registers are subaddressed. For example, to program DMA channel 0 registers, the value 0x00 (subaddress) is written to the DMSA register. The first value written to the DMSDI register is directed to the DMSCR0 register, the second value written to DMSDI is automatically directed to the DMDST0 register, and so on. However, if the value is written to the DMSDN register, the subaddress is not autoincremented, and only the particular register (specified in the DMSA register) is modified. A detailed description of the DMA register can be found in [2].

The DMA channel priority and enable control register (DMPREC) (located at address 54h) selects the DMA channels, controls the multiplexed interrupts, and controls the channel priorities. Because the DMA controller resets each enable bit after a block transfer, DMPREC can also be polled to determine whether the block transfer for a given channel has been completed. Each DMA channel can be assigned with only two priorities (low or high), where the high-priority channel is serviced before the low-priority channel. When multiple channels with high priority are selected, these channels are serviced in a round-robin fashion from low to high channel number. Detailed bit-field descriptions of the DMPREC are given in Table C.12.

In addition, the DMPREC register controls how DMA interrupts are assigned in the interrupt vector and IMR (interrupt mask register)/IMF (interrupt mask flag) registers. Due to the limited number of interrupts available in the C54x memory map, some DMA interrupts are multiplexed with other peripheral interrupts. Therefore, the interrupt multiplex control bits (INTOSEL) field in the DMPREC register provides a means of selecting the desired DMA channel interrupt. An example for the C5402 processor is displayed in Table C.13, which shows the bit value of the INTOSEL to select the DMA interrupt for channels 1 to 3.

# Appendix C Peripheral Programming for Digital Signal Processors

| Address | SubAddress | Name   | Function                                       |

|---------|------------|--------|------------------------------------------------|

| 54h     | —          | DMPREC | Channel Priority and Enable Control Register   |

| 55h     | _          | DMSA   | Subbank Address Register                       |

| 56h     | —          | DMSDI  | Subbank Access Register With Autoincrement     |

| 57h     | _          | DMSDN  | Subbank Access Register Without Autoincrement  |

| —       | 00h        | DMSRC0 | Channel 0 Source Address Register              |

| —       | 01h        | DMDST0 | Channel 0 Destination Address Register         |

| —       | 02h        | DMCTR0 | Channel 0 Element Count Register               |

| _       | 03h        | DMSFC0 | Channel 0 Sync Select and Frame Count Register |

| —       | 04h        | DMMCR0 | Channel 0 Transfer Mode Control Register       |

| —       | 05h        | DMSRC1 | Channel 1 Source Address Register              |

| _       | 06h        | DMDST1 | Channel 1 Destination Address Register         |

| _       | 07h        | DMCTR1 | Channel 1 Element Count Register               |

| —       | 08h        | DMSFC1 | Channel 1 Sync Select and Frame Count Register |

| —       | 09h        | DMMCR1 | Channel 1 Transfer Mode Control Register       |

| —       | 0Ah        | DMSRC2 | Channel 2 Source Address Register              |

| _       | 0Bh        | DMDST2 | Channel 2 Destination Address Register         |

| —       | 0Ch        | DMCTR2 | Channel 2 Element Count Register               |

| —       | 0Dh        | DMSFC2 | Channel 2 Sync Select and Frame Count Register |

| —       | 0Eh        | DMMCR2 | Channel 2 Transfer Mode Control Register       |

| —       | 0Fh        | DMSRC3 | Channel 3 Source Address Register              |

| —       | 10h        | DMDST3 | Channel 3 Destination Address Register         |

| _       | 11h        | DMCTR3 | Channel 3 Element Count Register               |

| —       | 12h        | DMSFC3 | Channel 3 Sync Select and Frame Count Register |

| —       | 13h        | DMMCR3 | Channel 3 Transfer Mode Control Register       |

| —       | 14h        | DMSRC4 | Channel 4 Source Address Register              |

| —       | 15h        | DMDST4 | Channel 4 Destination Address Register         |

| —       | 16h        | DMCTR4 | Channel 4 Element Count Register               |

|         | 17h        | DMSFC4 | Channel 4 Sync Select and Frame Count Register |

| —       | 18h        | DMMCR4 | Channel 4 Transfer Mode Control Register       |

|         | 19h        | DMSRC5 | Channel 5 Source Address Register              |

| —       | 1Ah        | DMDST5 | Channel 5 Destination Address Register         |

|         | 1Bh        | DMCTR5 | Channel 5 Element Count Register               |

| —       | 1Ch        | DMSFC5 | Channel 5 Sync Select and Frame Count Register |

| TABLE C.11 | DMA Registers | (reprinted with | permission | from [2]) |

|------------|---------------|-----------------|------------|-----------|

|------------|---------------|-----------------|------------|-----------|

C20

(Continued)

| Address | SubAddress | Name   | Function                                        |

|---------|------------|--------|-------------------------------------------------|

| —       | 1Dh        | DMMCR5 | Channel 5 Transfer Mode Control Register        |

| —       | 1Eh        | DMSRCP | Source Program Page Address (all channels)      |

| _       | 1Fh        | DMDSTP | Destination Program Page Address (all channels) |

|         | 20h        | DMIDX0 | Element Address Index Register 0                |