# **TestBencher Pro**

# **User's Manual**

www.syncad.com

# TestBencher Pro Manual (rev 6.5A) copyright 1994-1999 SynaptiCAD

#### **Trademarks**

- Timing Diagrammer Pro, WaveFormer Pro, TestBencher Pro, VeriLogger Pro, DataSheet Pro, and SynaptiCAD are trademarks of SynaptiCAD Inc.

- Pod-A-Lyzer is a trademark of Boulder Creek Engineering.

- PeakVHDL and PeakFPGA are trademarks of Accolade Design Automation Inc.

- V-System and ModelSim are trademarks of Model Technology Incorporated.

- Viewlogic, Workview, and Viewsim are registered trademarks of Viewlogic Inc.

- Timing Designer and Chronology are registered trademarks of Chronology Corp.

- DesignWorks is a trademark of Capilano Computing.

- Mentor and QuickSim II are registered trademarks of Mentor Graphics Inc.

- OrCAD is a registered trademark of OrCAD.

- PSpice is a registered trademark of MicroSim.

- Windows, Windows NT, and Windows 95/98 are registered trademarks of Microsoft.

All other brand and product names are the trademarks of their respective holders.

Information in this documentation is subject to change without notice and does not represent a commitment on the part of SynaptiCAD. Not all functions listed in manual apply to Timing Diagrammer Pro or WaveFormer Pro. The software and associated documentation is provided under a license agreement and is the property of SynaptiCAD. Copying the software in violation of Federal Copyright Law is a criminal offense. Violators will be prosecuted to the full extent of the law.

No part of this document may be reproduced or transmitted in any manner or by any means, electronic or mechanical, including photocopying and recording, for any purpose without the written permission of SynaptiCAD.

For latest product information and updates contact SynaptiCAD at:

web site: http://www.syncad.com email: sales@syncad.com phone: (540)953-3390

# **Table of Contents**

| Table of Contents                                           | 3  |

|-------------------------------------------------------------|----|

| Introduction                                                | 7  |

| Chapter 1: A Quick Start to TestBencher Pro                 | 9  |

| Step 1: Pick A Language                                     |    |

| Step 2: Add the MUT to the Project                          |    |

| Step 3: Add Signals to a Transaction Diagram                |    |

| Step 4: Draw First Transaction                              |    |

| Step 5: Add Transaction Diagram to the Project              |    |

| Step 6: Add Top-Level Template File                         |    |

| Step 7: Instantiate MUT in the Template                     |    |

| Step 8: Insert Diagram Calls into Template                  |    |

| Step 9: Generate the Test Bench                             |    |

| Step 10: Simulate Test Bench                                |    |

| Step 11: Finding Out More About TestBencher Pro             |    |

| Chapter 2: Project Functions                                |    |

| 2.1 Opening, Saving, and Starting New Projects              |    |

| 2.2 Project Preferences Dialog                              |    |

| , c                                                         |    |

| 2.3 Adding Files and Building the Project                   |    |

| 2.5 ModelSim Integration                                    |    |

| 2.6 Using a Third Party Simulator with TestBencher Projects |    |

|                                                             |    |

| Chapter 3: Create Transaction Diagrams                      |    |

| 3.1 Transaction Diagram Objects                             |    |

| 3.2 Direction and Type of Signals                           |    |

| 3.3 Driving Bi-directional Signals                          |    |

| 3.4 Creating Clocked Signals                                |    |

| 3.5 Creating Continuous Setups and Holds                    |    |

| 3.6 Variables in Timing Diagrams                            |    |

| 3.7 Delays and the Delay Properties Dialog                  |    |

| 3.8 Specifying a Timeout for a Delay                        | 26 |

| Chapter 4: Samples                                          | 2  |

| 4.1 Point Samples                                           | 27 |

| 4.2 Window Samples                                          | 27 |

| 4.3 The Sample Properties Dialog                            |    |

| 4.4 Self-testing Code from Samples                          | 28 |

| 4.5 Writing User-Defined Sample Conditions and Actions      |    |

| 4.6 Sample Values as Transaction Outputs                    |    |

| 4.7 Creating New Sample Types                               | 31 |

| Chapter 5: Markers                                          | 33 |

| 5.1 Adding a Marker to a Diagram                            |    |

| 5.2 Absolute and Relative Markers                           |    |

| 5.3 Time Markers for Specifying End Diagram                 |    |

| 5 4 Time Markers for Test Bench Loops                       | 34 |

| 5.5 HDL Code Markers                                           | 35 |

|----------------------------------------------------------------|----|

| Chapter 6: Diagram Level Test Bench Settings                   | 37 |

| 6.1 The Diagram Level TestBench Settings Dialog                | 37 |

| 6.2 Including External HDL Code Library Files                  |    |

| 6.3 Enabling/Disabling HDL Code for Parameters                 |    |

| 6.4 Specifying a Timeout for a Transaction                     |    |

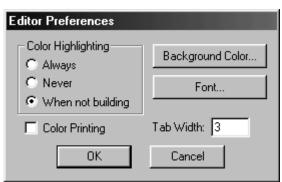

| Chapter 7: Editor Functions                                    |    |

| 7.1 Opening, Saving, and Creating New Source Code              |    |

| 7.2 Displaying or Finding a Specific Line of Code              |    |

| 7.3 Using the Editor Preferences Dialog                        |    |

| 7.4 Editor Cursor Commands                                     |    |

| -                                                              |    |

| Chapter 8: Working with Template Files                         |    |

| 8.1 Adding the Template to a Project                           | 45 |

| 8.2 Instantiating your Model Under Test (MUT)                  |    |

| 8.3 Using Diagram Calls to Trigger Transactions                |    |

| 8.5 Controlling the Execution Mode of a Transaction            |    |

| 8.6 Aborting a Timing Transaction                              |    |

| 8.7 Adding HDL Code to Template Files                          |    |

| Chapter 9: Generating the Test Bench                           | 51 |

| 9.1 TestBencher Pro Design Flow                                |    |

| 9.2 Generate the Test Bench                                    |    |

| 9.3 Errors During Test Bench Generation                        |    |

| 9.4 Simulating the Test Bench                                  |    |

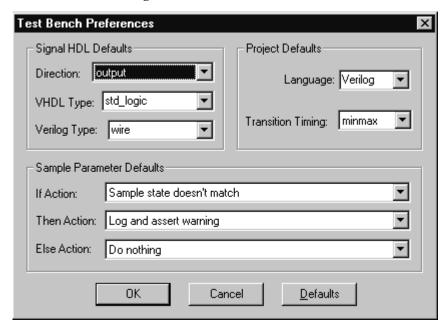

| 9.5 Test Bench Preferences Dialog (options)                    | 53 |

| Chapter 10: Advanced Techniques                                | 55 |

| 10.1 Generating Test Bench-Level Glue Logic                    | 55 |

| 10.2 Creating a Global Clock                                   |    |

| 10.3 Loops in Transactions                                     | 56 |

| Chapter 11: The Architecture of TestBencher Test Benches.      | 57 |

| 11.1 Files Used to Build a Project                             |    |

| 11.2 Status Signals and States                                 | 57 |

| 11.3 Monitoring Transaction Execution                          |    |

| 11.4 Generated Tasks for Timing Transactions                   |    |

| 11.5 TestBencher HDL Library Files                             |    |

| Appendix A: TestBencher Pro Basic Tutorial                     | 61 |

| 1 Setting up the Project                                       |    |

| 2 Creating a TestBencher Pro Timing Diagram                    |    |

| 3 Creating and Modifying a Template File                       |    |

| 4 Generate and Examine the Test Bench                          |    |

| -                                                              |    |

| <b>Appendix B: Performing a Sweep Test (Advanced Tutorial)</b> |    |

| 1 Create a Global Clock Generator with Adjustable Period       | 79 |

| Index                                                    | 93 |

|----------------------------------------------------------|----|

| Appendix C: License Agreement                            | 91 |

| 9 Generating the Test Bench and Simulating the Project   | 88 |

| 8 Adding HDL Code to Sweep the Delay                     |    |

| 7 Applying Timing Transactions to the Template File      |    |

| 6 Examine the Write Transaction                          | 84 |

| 5 Add a Continuous Setup Checker to the Read Transaction |    |

| 4 Add Sweepable Delay                                    | 82 |

| 3 Change Read Transaction to be Cycle Based              | 80 |

| 2 Add Global Clock as an Input to the Read Transaction   | 80 |

# Introduction

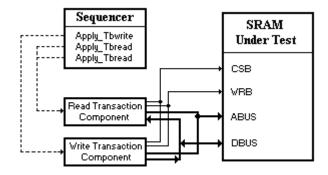

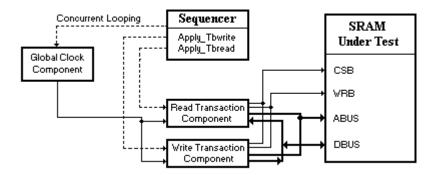

TestBencher Pro is a self-testing test bench generator for VHDL and Verilog. Test benches generated by TestBencher Pro include input stimulus vectors and extra code that checks simulation output for correctness. The generated test benches are capable of applying different stimulus vectors depending on simulation response so that the test bench functions as a behavioral model of the environment in which the system being tested will operate. Using TestBencher Pro, bus-functional microprocessor interfaces can be modeled with only a few lines of code. TestBencher Pro also provides an automated method for checking large ASIC simulation runs.

The quickest way to learn how to use TestBencher Pro is to work through the tutorials provided in the appendices and to read through Chapter 1: A Quick Start to TestBencher Pro. Advanced features such as global clocks, loops in test benches, building glue logic, generating code from samples, and controlling execution using markers can be found in the later chapters. There are also several test bench examples that are located in the \Examples subdirectory of the installation directory.

Additional information regarding the architecture and design flow when working with TestBencher Pro are available at the SynaptiCAD website (www.syncad.com).

8 Introduction

# Chapter 1: A Quick Start to TestBencher Pro

This chapter will cover all the basic steps involved in generating a bus-functional test bench using TestBencher Pro. More detailed information is available in chapters 2-9.

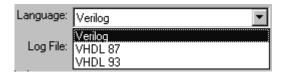

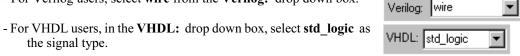

# Step 1: Pick A Language

The first step in creating a test bench is to choose the generated language. TestBencher Pro supports Verilog, VHDL 87, and VHDL 93. It is important for VHDL users to choose the VHDL standard that is compatible with your VHDL simulator and your existing model code. As TestBencher receives information on your model code and transaction diagrams it will incrementally generate code, so it is beneficial to choose the language at the beginning of the design. Choose the language for the current project:

- Choose the **Project > Project Settings** menu option to open the *Project Settings* dialog.

- Choose a language from the **Language** drop-down list box and then click **OK** to close the dialog.

To set the default language for all future projects:

- Choose the **Options** > **Test Bench Preferences** menu option to open the *Test Bench Preferences* dialog.

- Choose a language from the Language drop-down list box and then click **OK** to close the dialog.

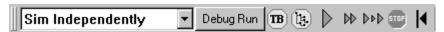

Another Project setting that must be set before you begin is the Simulation Mode. There are two different modes that TestBencher works in, Debug Run and Auto Run. The Debug Run mode allows you to control when the simulation is run. This is the best setting to use while you are developing your timing diagrams. The Auto Run mode runs the simulation every time a signal is modified or added. This mode works best when you are making small changes to a timing diagram, once all of the signals are in place. While designing your timing diagrams, you also want to begin with the **Simulate Project** setting selected while developing your first timing diagram.

To set your Simulation Mode and State:

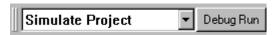

- If the mode button is set to **Auto Run**, click the button to toggle to **Debug Run**. The mode button is located on the simulation toolbar, below the **Project** menu in TestBencher.

- If the simulation state in the drop down list box is set to Sim Diagram & Project, select Simulate Project from the drop down menu. The drop down list box is located on the simulation toolbar beneath the File menu in TestBencher.

# **Step 2: Add the MUT to the Project**

TestBencher uses a project to control the test bench generation, set the transaction diagrams, and set the template files. The first thing to add to the project is the *model under test*, MUT, files of the design you wish to test. TestBencher will scan these files and copy the top-level signal information to the *Diagram* window. To add a file to the project:

- Right click in the Project window to open the context menu, and select the Add HDL File(s) menu option,

- OR, choose the **Project > Add HDL File(s)** menu option.

- Both of these functions open a file dialog. Select the files that you would like to add to the project and click the **Open** button to close the dialog.

Notice that the file names are listed in the project window. The source code can be viewed by double clicking on the file name.

# **Step 3: Add Signals to a Transaction Diagram**

Once the MUT has been added, the test bench signals that interface to the model under test need to be defined.

Add signals and edit the name, direction, and bit width to match the model under test:

- Add signals manually by pressing the Add Signal button.

- Double click on the signal name in the signal label window to open the Signals Properties dialog.

- Edit the signal **name**, **direction**, and bit width (**MSB** & **LSB**) fields. Signal direction is specified relative to the test bench, not relative to the model under test (e.g., a signal that is an input to a transaction is driven elsewhere in the model). Generally you will want to add signals that match the ports of your MUT, but in more complex transactions you may want to add internal signals that are only used by your transaction and do not directly interface to your MUT.

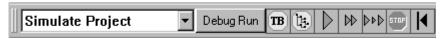

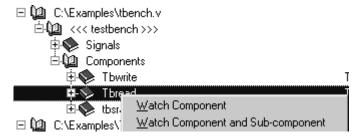

Once the project is built you can view all the modules, signals, ports, and components in the Verilog files. One module name will be surrounded by brackets << name>>>. This is the top-level module for the project. It is the highest-level instantiated component. All sub-modules can be viewed by descending the top-level module's tree.

If the top-level module does not have port signals, the internal signals of the module are displayed in the diagram. If the top-level module has port signals, the output ports are viewed as blue signals and input ports are viewed as black signals. The black input signals can now be edited to create a transaction model.

# **Step 4: Draw First Transaction**

In the next two steps you will draw and add a timing transaction for your test bench project. These steps will be repeated for each timing transaction in your project.

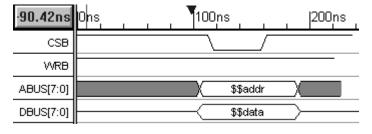

A timing transaction is a timing diagram that represents a reusable interface specification of the bus-functional model that you are creating (e.g., read cycle, write cycle, interrupt cycle). Timing diagrams are created using the built in timing diagram editor and Chapter 3 covers the more advanced features. The bus functional model code is generated from the waveforms, samples, markers, and variables that are contained in the timing diagram.

Specify the following information in each timing diagram:

- The **direction** and **type** (Section 3.2) of each signal is set using the *Signal Properties* dialog box. For example, SIG1 might have a direction of "output" and a type "integer". The direction of transition for **bi-directional** signals (Section 3.3) can be set using the Driven flag in the *Edge* dialog (double click left on the edge to open this dialog box).

The following optional components can be added to each diagram as desired:

- Variables (Section 3.6) can be defined for the timing diagram. A variable for a specific data bus gives you the option of using caller-specified state values for the data bus.

- Attach samples to the diagram to generate **self-testing** (Section 4.4) code. This type of code monitors the simulation and will perform as specified by the user (e.g., provide a warning message when the output is not what is expected). Sample actions may be from the library set, or they may be **user-defined** (Section 4.5).

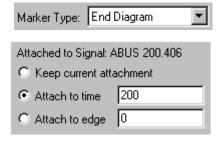

- An **End Diagram Time Marker** (Section 5.3) can be used to indicate the exact end of the timing diagram's execution (this can be used for clock synchronization).

- **Loop Time Markers** (Section 5.4) can be placed in the diagram to indicate looping sections of the timing diagram.

Other optional components will be discussed in more detail later in this manual. You will be able to determine which optional components to add based upon the exact nature of your simulation.

# **Step 5: Add Transaction Diagram to the Project**

After the timing transaction is drawn, save it to a file and add the timing diagram to the project.

Save the timing diagram:

- Choose the File > Save Timing Diagram menu option to save the file. This opens the Save File dialog. Timing diagram files use a \*.tim file extension.

Add the timing diagram to the project:

- Right click in the signal label window and choose Add Diagram to Project from the context menu. This puts the timing diagram into the Project window and generates the HDL code for the diagram.

View Generated HDL Source Code:

- Right click on the timing diagram file name in the Project window and choose **Open...** from the context menu. This will open an editor window and display the associated HDL file. The HDL file has the same name as the timing diagram with a \*.v extension for Verilog or a \*.vhd for VHDL.

At this point you can either design additional transactions by modifying the current timing diagram and following the instructions in Step 4, or you can continue with the next few steps and design the top-level test bench. By working with the top-level test bench early in the design you will be able to test individual transactions before constructing the entire bus-functional model.

# Step 6: Add Top-Level Template File

This section will explain how to add a Top-level template file. The template file provides the top-level model for your test bench. You will instantiate your model under test and control the sequencing of your diagram transactions from this file. Step 7 will explain how to edit the template for the specific project you are developing.

To add a top-level template file to the project:

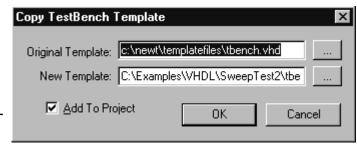

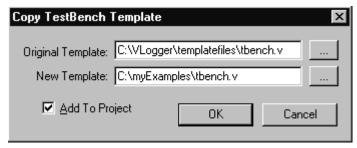

- Right click in the Project window and choose Copy TestBencher Template File from the context menu. This opens a dialog box with the same name.

- Check the Add to Project checkbox in the bottom left of the dialog box to ensure that the template you choose will be copied to the project.

- Enter an existing template file name into the **Original Template** edit box or use the Browse (...) button to find one on the hard drive. TestBencher Pro is shipped with two default template files for each language (found in the \templatefiles subdirectory of your TestBencher installation directory). Users can also design their own template files. If this is your first test bench, use **tbench.v** (for Verilog projects) or **tbench.vhd** (for VHDL projects) because it generates the simplest test benches.

- Enter the name for your top-level test bench into the **New Template** edit box.

- Click **OK** to copy the template and add it to the Project window.

# **Step 7: Instantiate MUT in the Template**

Next, you will add a code segment to the Template file that will instantiate the MUT in the test bench. Once the final test bench is generated it will become the top-level module in your design and will be responsible for instantiating the MUT and the timing transactions.

Open the template file and locate the place in the code to instantiate the MUT:

- Double click on the test bench file that was just added to your project. This opens an Edit window and displays the source code of the template file.

- Scroll through the template file and locate the following comment:

```

// 1) Instantiate Models Under Test after this comment block:

```

#### Verilog Users:

If you have already compiled the Verilog MUT, you can optionally use the project window to instantiate your MUT instead of manually typing the instantiation.

- Left click in the template file editor window below the comment shown above.

- Right click on the top level module (module name enclosed in brackets:

```

e.g., <<< module >>>) in the Project window to open the pop-up context menu

```

- Select Instantiate in TBench. This will add the instantiation of the selected module into the template file.

An example of instantiation of a MUT in Verilog is:

```

tbsram tbsram ( CSB, WRB, ABUS, DATABUS );

```

This line of code will declare your module for use in the project.

#### **VHDL Users:**

If you are using VHDL, instantiate the MUT by:

- Type the MUT instantiation into the template file. It will probably look something like this:

```

mutMSB: tbsram port map(CSB, WRB, ABUS, DBUS(15 downto 8));

```

- Next, scroll up in the code to the line

```

-- 1) Declare component for Models Under Test after this comment

```

Define the component portion of your module below this comment block. Use the following example as a model:

Note: Keep the Template file open for use in Step 8.

# **Step 8: Insert Diagram Calls into Template**

This step will show you how to place and sequence the transactions in the test bench.

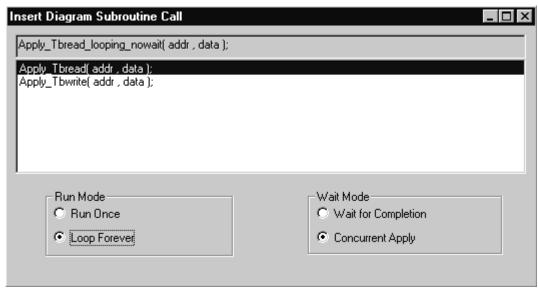

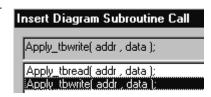

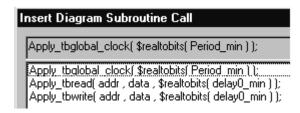

Use the *Insert Diagram Call* dialog to add timing diagram apply statements to the template file:

- Scroll down in the template file until you find the sequencer code. You will see a comment in the code that looks like:

- -- 4) Add apply calls for timing diagram transactions after this

- Left click in the template file just below this comment. This is the segment of code where timing transactions will be executed.

- Select Editor > Show Insert Diagram Call Dialog... This will open the Insert Diagram Call dialog. A list of statements will be in the dialog box. Each statement represents one of the timing transactions that you have added to the project.

- Double click on the first **Apply** *TransactionName* statement to add it to the template file.

- Notice that the Apply statement was inserted in the template file. The *Insert Diagram Call* dialog is a modeless dialog so you can leave it open while you perform other actions. Double clicking on additional Apply statements causes those statements to be added on successive lines.

- If any of the applied transactions contain variables, then edit the template code to provide values for variable names. In the example Apply statement below, a value of 3 is assigned to state Var.

```

// Apply verySimpleCyclic(stateVar)

Apply verySimpleCyclic(3);

```

See Section 8.3 Using Diagram Calls to Trigger Transactions for more information about adding diagram calls.

# Step 9: Generate the Test Bench

Once the Template file has been successfully edited, you are ready to generate the test bench. To do this:

- Choose **Export > Generate Test Bench** to generate the test bench.

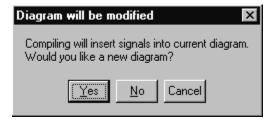

When the test bench is generated, several files are produced. One HDL file is produced for every timing diagram that you added to the project. Another HDL file is produced that represents the test bench itself.

The original template file contained a series of macros that are expanded to generate the HDL code for the test bench. In the template file, macros begin with a dollar sign (\$). The macros are used to expand the template file into the HDL code for the test bench file. This will be accomplished through direct textual substitution, resulting in the generated test bench.

The test bench can be generated repetitively, allowing you to make changes to the timing transactions without losing any code that you may have placed in the test bench. It is important to note that any text between the beginning and the ending of the macro comments will be replaced. This means that HDL code that you add should be placed before or after the blocks of code generated by TestBencher (see Section 9.2 for more information).

Two other files will be important during the test bench simulation (Step 10) - "verilog.log" and "waveperl.log". The first file will contain simulator warnings and errors that occur during the simulation. The Report window (lower right hand corner) has a tab on the bottom that is labeled "verilog.log". Click this tab to view "verilog.log." The second log file, "waveperl.log," will report warnings specified by the simulator. The test bench can be set up to record unexpected values, for instance. (Note: other files and reports that are available are listed under the other labeled tabs in the Report window.)

#### Step 10: Simulate Test Bench

The test bench that you have created can now be simulated by taking all of the files produced by TestBencher Pro and placing them into a simulator. Verilog users can use the information in this section to simulate the test bench using TestBencher Pro.

There are three ways to run the simulation:

- Press the Run button (large green triangle) on the simulation button bar, making sure the Simulate Project option is selected.

- Choose the **Simulate** > **Run** menu option, OR

- Press the **<F5>** key.

The waveforms will be displayed in the Diagram window once a project is simulated. If you do not want to continue to watch a particular signal, left click on the signal name in the Diagram window and press the **Delete** key.

TestBencher Pro has two simulation modes, **Auto Run** and **Debug Run**. These modes determine when a simulation is performed. The current simulation mode is displayed on the leftmost button on the simulation button bar; this is the *mode button*. In the **Debug Run** simulation mode, simulations are started only when the user presses the Run or Single Step buttons (similar to a standard Verilog simulator). In the **Auto Run** simulation mode, the simulator will automatically run a simulation each time a waveform is added or modified in the Diagram window. This mode makes it easy to quickly test small modules and do bottom-up testing. Press the mode button to toggle between the two simulation modes.

TestBencher Pro also has two simulation states, **Sim Diagram & Project** and **Simulate Project**, that determine what is simulated. The state can be selected by using the drop down list to the left of the mode button on the simulation button bar. The **Sim Diagram & Project** mode indicates that both the diagram waveforms and the Verilog source code will be simulated together. The **Simulate Project** state indicates that Verilog code and the diagram will be simulated independent of one another. The simulation button bar controls the simulation in this state. An additional method of controlling simulation is by use of the **Simulate Diagram** button on the simulation button bar. Waveforms cannot be used as stimuli in the **Simulate Project** state, and so they cannot be used to drive signals. The **Simulate Project** state gives the user the ability to perform timing and analysis on waveforms without incurring the overhead of re-simulating the entire project. This mode is often useful when creating transactions for a test bench.

# Step 11: Finding Out More About TestBencher Pro

The quickest way to learn more about using TestBencher is to perform the tutorials provided for the project and to examine the example files provided with the project. Appendices A and B of this manual provide a basic tutorial and a more advanced tutorial, respectively.

Additional example files can be found in the **Examples** subdirectory of the installation directory. Many of these files contain text in the timing diagram that specifies what the timing diagram demonstrates. In addition, there is a **readme.txt** file in the Examples directory that specifies the contents of each subdirectory of the **Examples > VHDL** and **Examples > Verilog** directories.

# **Chapter 2: Project Functions**

TestBencher Pro uses a project to list the files to be simulated, set watches on signals (view signal waveforms), and store simulation options.

# 2.1 Opening, Saving, and Starting New Projects

Projects are opened and saved using the Project menu options. By default, TestBencher opens with a new untitled project.

To open an existing project:

- Select the **Project > Open HDL Project** menu option. This opens the *Open Project File* dialog where you can select a project file to open.

To save an open project:

- Select the **Project > Save HDL Project** menu option to open a *Save* dialog. By default, project file names have an extension of **HPJ**.

To clear the current project and start a new project:

- Select the **Project > New HDL Project** menu option. You will be asked several questions about saving the files that are currently open and then a new project will be created.

# 2.2 Project Preferences Dialog

The *Project Settings* dialog controls the simulator run time options. This information is stored inside the project HPJ file. To open the *Project Settings* dialog:

- Choose the **Project > Project Settings** menu option to open the *Project Settings* dialog

There are several options in the *Project Settings* dialog.

- The **Delay Settings** radio buttons determines which delay value is used in **min:typ:max** expressions. This is similar to the +maxdelays, +mindelays, and +typdelays command line simulator options.

The next group of options are the checkboxes to the right of the **Delay Settings** section.

- The Grab top level signals check box turns on the automatic monitoring of ports or internal signals in the toplevel module.

- The **Show file tree nodes** check box allows file names to be shown in the project tree.

- The **Hide empty lists** check box hides nodes without any leaf nodes. Checking this makes the project tree more readable.

- The Capture and Show Watched Signals check box enables the display of waveform results from a simulation run..

- The **Dump Watched Signals** check box will generate a dump file for any watched signals in the diagram. The generated file will have the same name as the .tim file, only with an extension of .VCD.

- One setting in this dialog has been reserved for future use – the Interactive Mode After Compile checkbox.

Below these two groups are several edit boxes that tell the project where to look for files, the file types that are being used, etc. These options are explained below.

- **Include Directories** edit box specifies the directories where TestBencher searches for files that will be used in the project. The following is a Windows example (Unix users should use the / slashes):

C:\design\project;c:\design\

library

- The **Library Directories** edit box lists the path and directories where Test-

Figure 2.1: Project Settings dialog

Bencher searches for library files. TestBencher will try to match any undefined modules with the names of the files that have one of the file extensions listed in the **Lib Extensions** edit box. The simulator does not look inside a file unless the undefined module name exactly matches a file name. The simulator does not look at any files unless there are file extensions listed in the **Lib Extensions** edit box. The following is a Windows example (Unix users should use the / slashes):

C:\design\project;c:\design\library

- The **Lib Extensions** edit box specifies the file name extension used when searching for library files in the library directory. Each library extension should begin with the period character followed by the extension name. Use a semicolon to separate multiple file extensions.

. V; . VV

- The **Language** setting is controlled by use of a drop down list box. It is important that this setting be properly selected to ensure that the generated test bench is written in the correct language.

- The **Logfile** specifies the name of the log file which receives all the simulation results and information. By default TestBencher uses **verilog.log** file.

- The **Command Line Options** edit box contains the command line equivalents for all the options that are checked in this dialog. When the **Generate Command File** button is pushed, the text contained in the **Command Line Options** edit box along with the list of Verilog files specified in the project window are written to a command file. This file can then be used with the Command Line version of the TestBencher simulator.

If you work primarily with one language, you probably want to set a default language so that you do not have to reselect the language for each new project. When you have finished making the project settings with the *Project Settings* dialog box, you can change the default language for all future projects by:

- Choosing the **Options** > **Test Bench Preferences** menu option to open the *Test Bench Preferences* dialog.

- Choosing a language from the Language drop-down list box in the Project Defaults section of the dialog box and then clicking OK to close the dialog.

# 2.3 Adding Files and Building the Project

The first step in creating a project is to add timing diagrams to the project window.

If you need to create new timing diagrams, see Chapter 1: A Quick Start to TestBencher Pro for a quick start, or Chapter 3: Create Transaction Diagrams for a more detailed explanation.

If you have timing diagram files (.tim) already prepared, do the following to add them to the Project window:

- Right click in the Project window to open the context menu, and select the Add Timing Diagram(s) menu option,

- OR, choose the **Project > Add Timing Diagram(s)** menu option.

- Both of these functions open a File dialog. Select one or more files to add to the project and click the **Open** button to close the dialog.

To add an existing HDL file to the project:

- Right click in the Project window to open the context menu, and select the Add HDL File(s) menu option,

- OR, choose the **Project > Add HDL File(s)** menu option.

- Both of these actions open a File dialog. Select one or more files to add to the project and click the **Open** button to close the dialog.

Note: If you add a file to a project that has not yet been saved you will be prompted to save the new project. The Save New Project As dialog will open. The directory that you save the new project in will be the project directory, and all generated files will be placed in this directory.

Verilog users will be able to build the project for simulation under TestBencher. VHDL users will not be able to build the project within TestBencher, so a hierarchical view of the files will not be possible. When files are first added to the project, you can see the filename but you cannot see a hierarchical view of the modules inside the files. To view the internal modules on the project tree you must first build or run a simulation. The build command compiles the Verilog files and builds the Verilog tree. It does not run a simulation. For large projects, build lets you quickly construct the tree without having to wait for a simulation to run.

There are three ways to build a project:

- Press the yellow **Build** button on the simulation button bar,

- Select the Simulate > Build menu option,

- OR, press the <**F7**> key

Chapter 8: Working with Template Files gives a detailed explanation of working with Template files. Template files are used to generate the test bench itself once the timing transactions have been added to the project. The Template has a file extension of .v for Verilog users and .vhd for VHDL users. Once all of your timing diagrams have been completed, you will be ready to add your Template file to build the test bench.

To add a top-level template file to the project:

- Right click in the Project window and choose Copy TestBencher Template File from the context menu. This opens a dialog box with the same name.

- Check the Add to Project checkbox in the bottom left of the dialog box to ensure that the template you choose will be copied to the project.

- Enter an existing template file name into the **Original Template** edit box or use the Browse (...) button to find one on the hard drive. TestBencher Pro is shipped with two default template files for each language. Users can also design their own template file. The isotbench test bench generates the waveforms related to the MUT, while the tbench generates all of the waveforms that will let you see the exact status of each transaction during the simulation. The tbench is the default test bench template file because it provides more information and the file is simpler.

- Enter the name of your top-level project into the **New Template** edit box.

- Click **OK** to copy the template and add it to the Project window.

Once the Template file is in place and edited to include your MUT and timing transactions (Steps 1 & 8, Chapter 1: A Quick Start to TestBencher Pro), you can generate the test bench by selecting Export > Generate Test Bench...

If you are using Verilog, you can **build** the test bench using the **build** or **run** instructions above. After the project is built you can view all the modules, signals, ports, and components in the Verilog files. One module name will be surrounded by brackets << name>>. This is the top-level test bench module for the project. The top-level module is the highest level-instantiated component. All sub-modules can be viewed by descending the top-level module's tree. Section 9.4: Simulating the Test Bench discusses project simulation.

# 2.4 Using the Project Tree Control

The Project Tree control is used to investigate the hierarchical structure of the Verilog components, view source code, and set watches on signals. Each node in the tree has a context sensitive pop-up menu that can be opened by right clicking on the node. The following functions describe the general viewing features of the tree control.

Viewing source code:

- To open an HDL file: double click on a file name to open the file in a new editor window.

- To see the declaration of a signal or component: double click on the signal or component to jump to the declaration in the HDL source code.

Expanding or hiding branches of a tree:

- Click  $\oplus \bigotimes$  or  $\ominus \bowtie$  to expand or close a node. This will display but not open sub-nodes.

- To completely expand a node and all sub-nodes: right click on a node and choose **Expand Item** from the popup menu.

Figure 2.2: Project Tree control window

# 2.5 ModelSim Integration

If you use ModelSim to simulate either your Verilog or your VHDL code, you can enable the ModelSim Integration feature of TestBencher. The integration feature will cause ModelSim to launch with a library built and loaded for the project you are working with in TestBencher. This section describes how to enable ModelSim Integration as well as how to work with it.

#### **Enabling ModelSim Integration**

To enable ModelSim Integration:

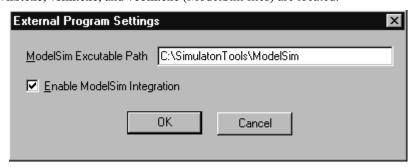

- Select the **Options > External Program Settings** menu option. This will open the *External Program Settings* dialog.

- Click the **Enable ModelSim Integration** checkbox. Once this checkbox is enabled, the project you are working with (Verilog or VHDL) will be simulated using the ModelSim simulator. Note: If you want to use the Verilog simulator provided with TestBencher Pro, this checkbox can not be checked.

- Enter the path to the executable directory for ModelSim in the ModelSim Executable Path. If you are able to execute ModelSim from any command prompt (that is, if the executable path is a part of your path in your account profile), then you do not need to enter an executable path. Otherwise, this should be the directory where the vlib.exe, vsim.exe, and vcom.exe (ModelSim files) are located.

#### Simulating with ModelSim Integration Enabled

The ModelSim Integration feature uses the project directory for your TestBencher project as the working directory for ModelSim. The ModelSim library associated with the project will have the same name as the project and will be built in a subdirectory of the project directory.

To build the ModelSim library and invoke the ModelSim simulator:

- Follow the normal steps to generating a top-level test bench (see Chapter 1: A Quick Start to TestBencher Pro for the steps to test bench generation).

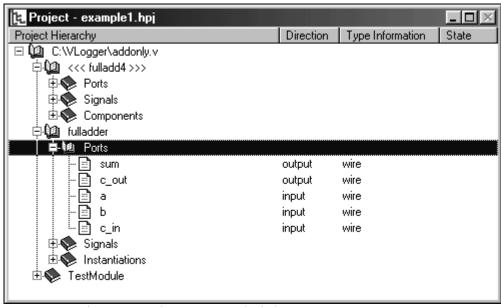

- Click the yellow TB button **TB** on the simulation button bar. This will copy the appropriate SynaptiCAD library files to your project directory and launch the simulator with the '-gui' switch and the '-do' switch. The .do file that will be invoked is the do file generated by TestBencher for the project. The .do file contains the commands to compile each of the appropriate library and source files, including the test bench file, into the project library being created. Upon successful compilation, it will load the testbench entity from the toplevel test bench.

Once the design is loaded into ModelSim, three windows will be opened automatically – the Structure, Signals, and Wave windows. Additionally, all of the top-level signals from the testbench entity and the status signal for each timing transaction (see Section 11.2: Status Signals and States for more information regarding status signals) will be placed in the Wave window. These signals will allow you to monitor the MUT and the transactions during simulation.

#### Behind the Scenes: Files Used for ModelSim Integration

The ModelSim Integration feature creates two extra files (in addition to the normal files generated by TestBencher) in your project directory when you generate the test bench. These files are projectName>.bat (projectName>.pl if you are using a UNIX based system) and **<projectName>.do**, where **<projectName>** is the name of your project.

The script file (.bat or .pl) file will copy any base library files (such as syncad.v or syncad.vhd) into your project directory, it will then launch the simulator with the directive to call the do command for the generated .do file. These files remain in the directory so that you can execute the .bat file manually at a later time to launch the simulator and load the library without going through the TestBencher interface. Simply go to the project directory and enter the project name at the command line, or double click the .bat file in the project folder if you are working in a Windows name>.pl" at the command line.

# 2.6 Using a Third Party Simulator with TestBencher Projects

A command file can be generated for a project that will be simulated using a third party simulator. This file can be used when the third party simulator is invoked from the command line.

#### To generate the command file:

- Select the **Project > Project Settings** menu option.

- Click the Generate Command File button.

- Enter the filename for the command file in the Filename edit box. (The file extension will be ".vc" by default.)

- Click the Save button to save the file.

To use this file with a third party simulator, you then use the '-f' switch followed by a space and then the filename entered above to simulate the project.

For example, consider a project named test. If the generated command file is named 'test.vc' this file would be used with VeriLogger's command line simulator using:

```

vlogcmd -f test.vc

```

# **Chapter 3: Create Transaction Diagrams**

Transaction diagrams are timing diagrams that represent reusable timing transactions (e.g., read cycle, write cycle, interrupt cycle). This chapter will discuss the components of a timing diagram and how they interact with TestBencher Pro.

When creating a timing diagram you will need to specify the following types of information:

- The **direction** and **type** (Section 3.2: Direction and Type of Signals) of each signal using the Signal Properties dialog box. For example SIG1 might have a direction of "output" and a type "integer". For bi-directional signals (Section 3.3: Driving Bi-directional Signals) the direction of transition can be set using the Driven flag in the Edge dialog (double click left on the edge to open this dialog box).

The following optional components can be added to each diagram as desired.

- Variables (Section 3.6: Variables in Timing Diagrams) can be defined for the timing diagram. A variable for a specific data bus gives you the option of using caller-specified state values for the data bus.

- Attach Samples (Chapter 4: Samples) to the diagram to generate self-testing (Section 4.4: Self-testing Code from Samples) code. This type of code monitors the simulation and will take action as specified by the user (e.g., provide a warning message when the output is not what is expected, or execute another timing diagram, as specified in the sample). Sample actions may be taken from the library set or they may be user-defined (Section 4.5: Writing User-Defined Sample Conditions).

- An End Diagram Time Marker (Section 5.3: Time Markers for Specifying End Diagram) can be used to indicate the exact end of the timing diagram's execution (good for clock synchronization).

- Loop Time Markers (Section 5.4: Time Markers for Test Bench Loops) can be placed in the diagram to indicate looping sections of the timing diagram.

You will be able to determine which of the optional components to add based upon the exact nature of your simulation.

# 3.1 Transaction Diagram Objects

Using the built-in timing diagram editor you will draw timing diagrams that represent reusable timing transactions (e.g., read cycle, write cycle, interrupt cycle). Timing diagrams are drawn using the Signal Button bar (see Figure 3.1). The first group of four buttons (left) are used to add signals, clocks, buses, and spacers to your diagram. The next group of six are used to add objects (i.e., markers and samples) to the diagram. The remaining buttons are used to create the waveforms for the signals.

Figure 3.1: Signal Button Bar

#### To add a Signal, Clock, Bus or Spacer:

- Left click the appropriate button in the first group of four. This will add the Signal, Clock, Bus or Spacer to the timing diagram.

- If you added a signal, clock or bus, double click the name of the new object to set the properties for that object. Signals and buses need to have the direction and type specified. They may also need to have waveforms drawn.

#### To Draw a Waveform:

- Left click the type of state that you want to add in the group of 7 states on the right side of the Signal Button bar.

- Left click in the waveform section of the timing diagram editor to the right of the signal or bus name at the approximate time that you want the state transition to occur. This will place the transition in the waveform. Waveforms are built from left to right.

- Repeat the first two steps until you have completed the signal's waveform.

The other items that can be placed in the timing diagram will be discussed later in this chapter. The Timing Diagram Editor manual provides in depth information for the use of the Timing Diagram editor (an online version of this manual is provided with TestBencher).

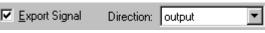

# 3.2 Direction and Type of Signals

The generated test bench provides stimulus and monitors simulation outputs of the circuit that you are designing. In order to do this, the signals that will be exported to the test bench have to match the signals that exist in your designs. If the signals in the test bench are named the same as in your circuit model then the matching will be automatic. If the signal names are different you will have to specify the mapping in MUT instantiation in the template file.

The type and direction of signals must also be compatible between the test bench and the circuit under test. To change the type and direction of signals in the test bench:

- Double left click on the signal name to open the Signal Properties dialog box. Make the necessary changes using the drop down list box titled *Direction* and click the OK button to close the dialog.

TestBencher Pro supports special output directions that specify how these signals work when more than one timing diagram tries to drive them. The default direction is output.

The following describes direction options and their meanings with respect to the test bench.

- Shared output continues to be driven after a timing diagram finishes. If more than one timing diagram attempts to drive the signal then the last timing diagram to drive wins.

- Output is only driven while that particular timing diagram is active. When the timing diagram finishes, the signal is automatically tri-stated (Note that this setting will only work with data types that support tri-stating).

- Persistent output continues to be driven after a timing diagram finishes. If more than one timing diagram attempts to drive a signal then a simulation conflict will occur. This will be either be resolved by the conflict tables of the simulator or will cause a simulation error to occur.

- Input is what you expect the circuit under test to generate during simulation (these signals are inputs to the timing transactions, driven by the model under test). In the timing diagram, Sample parameters usually end on an input signal, indicating that the input signal should be checked for an expected value at that point on the signal.

- Inout indicates that the signal is bi-directional (see section 3.3). Inout signals contain driven and un-driven signal segments. Driven segments act similar to signals of type **output**.

- Persistent inout indicates that the signal is bi-directional. The driven segments of the signal act like signals of type persistent output.

# 3.3 Driving Bi-directional Signals

For Bi-directional signals you must choose the inout direction and then indicate which segments on the signal waveform are inputs.

Set the direction of the signal to either **inout** or **persistent inout**:

- Double left click on the signal name to open the Signal Properties dialog box. Choose one of the **inout** directions and click the **OK** button to close the dialog.

\_ \_ X

All the segments on the signal are assumed to have a direction of either output or persistent output and are colored black to indicate their direction. To change a segment to be an input segment (un-driven):

- Double left click on the right-hand edge of the input segment. This opens the Edge Properties dialog box.

- Uncheck the Driven check box. This indicates that the test bench does not drive the segment to the left of the edge. This segment will be an input to the test bench.

- Click OK to close the dialog or use ALT-N or ALT-P to edit other edges on the same signal. The segment for which you unchecked the driven flag should now be colored blue. If the segment is not blue then make sure that the signal's direction is set to either inout or persistent inout by double clicking on the signal name.

Signal Properties

If you are working with a simulation, you will see that TeshBencher creates a second signal for any bi-directional signal you have entered. This created signal and its waveform appear in pink (or red) with the same name as the signal you created. The waveform for this signal will show you exactly what the signal is doing during the course of the simulation.

# 3.4 Creating Clocked Signals

By default, the events on a signal are delayed relative to the beginning of the timing diagram. However, signals can be made relative to a clock or to another signal's edges. The difference is that instead of edge transitions occurring at an absolute time, as with unclocked signals, the edge transition will occur relative to the edges of the signal (or clock) that they are clocked from. In this manner, the edge transitions use relative time instead of absolute time.

#### To create a clocked signal:

- Double click the signal name in the signal window to open the Signal Properties dialog (see Figure 3.2).

- Select a signal name from the **Clock** drop-down list

- Use the Edge/Level drop-down list box to specify which clock action will cause an event on the sig-

- Click **OK** to close the *Signal Properties* dialog.

The options listed under the Edge/Level list box allow you to decide which clock values will affect the signal, where Neg and Pos refer to the respective edges, high and low refer to the clock value, etc.

#### Name: SIG0 Active Low Simulate Once Analog Props Grid Lines C Simulate Drive O Watch Compare Boolean Equation: ex. (SIG1 and SIG2) delay 5 • Clock: Unclocked Edge/Level: neg • Not Used Clear: Not Used • Clock Enable: Not Used Advanced Register Boolean Equation Verilog. O VHDL 8ns=Z (5=1 5=0)\*5 9=H 9=L 5=V 5=> Wfm Egn Label Egn Hex(Inc(0,2,5)) Export Signal Direction: | output • Analog Display Size Ratio: 1 VHDL: std logic Verilog: wire • Radix: hex Bus MSB: 0 LSB: 0 OK. Cancel Apply

Figure 3.2: Signal Properties dialog

#### **Editing Multiple Signals**

Using this feature, you will often want all of the signals in a given timing diagram to be clocked in the same manner. To accomplish this, make sure the Signal Properties dialog is closed. Then:

- Select all of the signals you want to be clocked signals by left clicking the signal names in the signal window.

- Right click one of the highlighted signal names and select **Edit Selected Signal(s)** from the pop up menu.

- Select the clock signal name from the **Clock** drop-down list box.

- Specify which clock action will cause an event on the signal using the Edge/Level drop-down list box.

- Click **OK** to close the *Signal Properties* dialog.

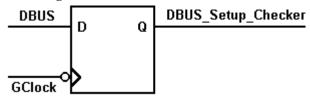

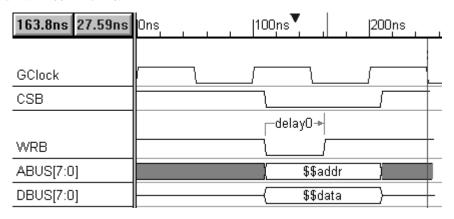

# 3.5 Creating Continuous Setups and Holds

Continuous Setups and Holds can be created for any clocked signal in TestBencher Pro. This section will describe how to create a continuous setup or hold that will persist for the duration of the timing transaction execution.

#### To Create a Continuous Setup or Hold:

- Double left click on a signal name to open the Signal Properties dialog.

- Choose the Clocking signal from the **Clock** drop-down list box. The clocking signal can be any clock or signal in the timing diagram.

- Choose the type of edge or level triggering from the Edge/Level list box. For a Register circuit, choose neg for

negative edge triggering, pos for positive edge triggering, or both for edge triggering. For a Latch circuit

choose either low or high level latching.

- The **Set**, **Clear**, and **Clock Enable** are optional signals that model the set, clear, and clock enable lines of the register or latch. If "Not Used" is chosen for a line, then that line is not modeled. These lines can be active low or high and synchronous or asynchronous depending on the settings in the Advanced Register and Latch Controls dialog (see next bullet).

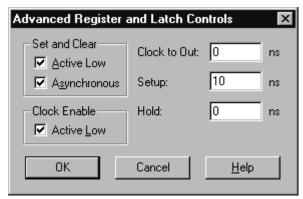

- The **Advanced Register** button opens the *Advanced Register and Latch Controls* dialog (see Figure 3.3) that determines how this individual register is generated. The global defaults can be defined using the **Options** > **Simulation Preferences** menu. This dialog controls the following options:

- Clock to Out: Describes the delay from the triggering of the clock signal to a change on the output edge.

- **Setup**: Describes the time for which the input must be stable before the clock-triggering event. If a **min/max** time pair is entered, **Setup** will use the **min** time. Any violations of this setup time will be reported to the simulation log file verilog.log, shown in the report window.

- **Hold**: Describes the time for which the input must remain stable after the clock-triggering event. If a **min/max** time pair is entered, **Hold** will use the **min** time. Any violations of this hold time will be reported to the simulation log file verilog.log, shown in the report window.

- Clock Enable Active Low: If checked, the clock will be enabled when the clock enable line is low. If unchecked, the clock will be enabled when the clock enable line is high.

- **Set and Clear Active Low**: If checked, the set and clear lines will control the output when they are low. If unchecked, then the set and clear lines will control the output when they are high.

- Set and Clear Asynchronous: If checked, then the set and clear lines will control the output anytime they are active. If unchecked, the model is synchronous and an active set or clear line does not affect the output until the next clock trigger event.

Figure 3.3: Advanced Register and Latch Controls

# 3.6 Variables in Timing Diagrams

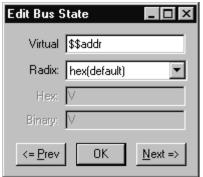

Variables inside timing diagrams can assume a new value each time the diagram is called. This is convenient for timing diagrams that have data and address buses because each time the diagram is called new values can be passed into the timing diagram.

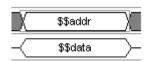

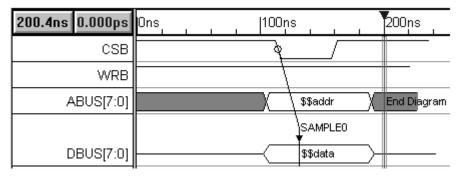

The procedure for specifying a state variable is similar to that of specifying a constant state value for a signal segment. State variables begin with two dollar signs, such as \$\$name. This name should be entered in place of the constant value for the signal segment. Variables are added to represent the value of a signal segment.

#### To add a variable signal segment:

- Double click on the segment of the signal in which you want to place the variable to open the Edit Bus State dialog.

- Type the variable name into the Virtual edit box. For example, \$\$data might be the name of the variable for the value of data bus.

- Click **OK** to close the dialog box.

You will pass the variable's value in to the timing diagram using the **Apply** TransactionName call in the template file. This is covered in Section 8.3: Using Diagram Calls to Trigger Transactions.

# 3.7 Delays and the Delay Properties Dialog

A delay specifies a fixed time between two signal transitions. Both the **min** and **max** values of the *Delay Properties* dialog are used in defining delays. One potential use for delays would be to create a handshaking mechanism between the MUT and a timing transaction.

The HDL code generated for a Delay is a process that will wait for a specific edge transition to occur (the forcing edge). Once this edge has transitioned, then the process will wait for the amount of time specified, and then the delayed transsition will occur. The Enable HDL Code checkbox in the Delay Properties dialog must be enabled for the code to be generated.

#### To add a Delay to a Timing Diagram:

- Left click the **Delay button** to turn the button red.

- Left click on a transition to select it. For a delay this is the forcing transition. For a setup or hold this is the transition that will be monitored.

- Right click on the second transition to add a parameter between the first and second transitions. For a delay this is the transition that will be moved. For a setup or hold this is the control signal.

The delay will be drawn in the timing diagram between the two specified edges. A default name is assigned to the delay. If you want to change the delay's name, you can do so through the Delay Properties dialog.

The Delay Properties dialog is used to control the property settings of an individual delay. Open this dialog by:

- Place a delay in the timing dialog.

- Double left click the name of the delay. This will open the *Delay Properties* dialog.

#### The settings that you need to specify are:

- Min: sets a minimum time to be used for the delay.

- Max: sets a maximum time to be used for the delay.

- The **Is Apply Subroutine Input** checkbox allows you to generate ports between the test bench and the timing transaction with which to specify the values to use for the min and max settings of the delay.

- The Enable HDL Code Generation allows you to turn the code generation on and off without removing the delay from the timing diagram. This checkbox must be checked in order to produce any HDL code for the sample.

Note: The HDL code generation for all delays in a timing diagram can be disabled through the Diagram-Level Test Bench Settings dialog. See Section 6.1: The Diagram Level Test Bench Settings Dialog for more information on this feature.

The HDL Code button will open the HDL Code For Delay dialog. This dialog can be used to set a timeout for the delay. This timeout will cause the delay to timeout after the specified time, at which point the Timeout Action specified in this dialog will occur. The default Timeout Action is that the edge transition will occur.

#### Using the Min and Max Settings

The Project Settings dialog controls how the min and max properties will be used by TestBencher. The **Delay Settings** option in the *Project Settings* has three radio buttons:

- Min: if this option is selected, the min value provided in the delay settings will be used for the delay value.

- Typical: this option will average the min and max settings for the delay to determine the delay value.

- Max: this option will use the max value setting to provide the delay value.

If only one of the two settings has been given a value (min or max), the other setting will internally be given the same value.

# 3.8 Specifying a Timeout for a Delay

Delays can be given a default action in the event of a timeout to ensure that the edge transition occurs. This timeout can be set using the HDL Code button in the Delay Properties dialog. When this button is clicked, the HDL Code for Delay dialog opens.

The two items to be specified in this dialog are the **Timeout** value and the **Timeout Action**. The **Timeout** value is the time that a delay process will wait for the forcing edge transition to occur. If a timeout is specified, then the HDL code will wait for the forcing edge transition or for the amount of time specified, whichever comes first. The **Timeout** Action will determine the action that will be taken if the timeout occurs first. The default action is that the edge transition will occur.

# **Chapter 4: Samples**

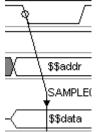

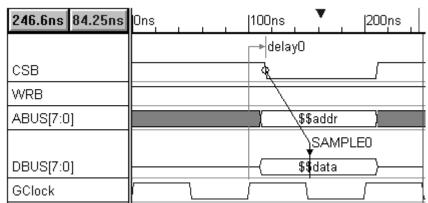

Sample parameters generate self-testing code in the test bench. Samples are normally used to monitor the signal values coming back from the model under test. Samples can test the value of a signal at a specific time or at a time relative to an event on another signal. The value that is the result of a sample can be exported to the top-level module. This could be used, for instance, to provide an input value for a state variable in another timing transaction or to determine if a specific timing transaction is to be executed or not.

# 4.1 Point Samples

Point samples are used to test or report the value of a given signal at a given time. The time selected for the sample to occur may be absolute or relative.

#### **Absolute Samples**

Absolute samples are set to sample at an absolute time. By doing this, the time that the sample is taken will not vary unless you specifically move it. To create an absolute sample, right click on the signal to be sampled to place the absolute sample.

#### **Input Relative Samples**

Samples that are set to sample within a set time after a diagram transition are called relative samples. Relative samples are created by left clicking on the relative edge and right clicking on a signal to be sampled. If a relative sample is relative to an input transition, the sample is called an Input-Relative Sample. When diagram execution gets to the beginning time of an input edge that has an Input-Relative Sample attached to it, the diagram suspends execution until the input transition occurs. This allows a sample to occur an exact time after an input transition, even though the time of the input transition may not be determined until simulation time. A relative sample is clocked off the edge of another signal, and so will move with that edge.

#### 4.2 Window Samples

Window samples are used to test the value of a signal over an interval of time. This feature is useful for testing that the value of a given signal does not change over a specified time frame, for reporting the value of the signal as it changes during a specified time, or for verifying that the signal goes through a specified sequence of states.

Windowed samples may also be absolute or relative (see *Section 4.1: Point Samples* for more information about absolute and relative samples).

#### To create a windowed sample:

- Left click the sample button Sample on the Simulation Button Bar.

- If you want the sample to be relative, left click the edge that you want the sample to be relative to.

- Right click on the signal to be sampled. Note that you can place the sample at either the beginning time that you want the window sample to use or the ending time.

- Double click the sample name to open the Sample Properties dialog.

- Type the beginning sample time into the Min: edit box of the Sample Properties dialog.

- Type the ending sample time into the Max: edit box of the Sample Properties dialog.

#### 4.3 The Sample Properties Dialog

The *Sample Properties* dialog is used to set the properties of a given sample. This dialog is discussed more thoroughly in the Timing Diagram Editor Help. This section will give a brief overview of the various options in the dialog.

- The **Enable HDL Code Generation** checkbox must be checked for any code to be generated for the sample.

- The **HDL Code** button will be discussed in *Section* 4.4: Self-testing Code From Samples.

- The **Min:** and **Max:** edit boxes are used to specify the beginning and ending times for a sample window.

- The **Display Label** drop down menu allows you to select what text will be displayed for the sample.

- The **Library** button will open the parameter library. This library can be used to modify certain properties. By double left clicking on a field in the library, the property dialog for the parameter indicated will open so that you can modify the value of that field.

- The **Prev** and **Next** buttons can be used to move from one parameter to the next (forwards or backwards on the parameter list).

The HDL code generation of Samples can be enabled and disabled using the diagram level test bench settings (see Section 6.3: Enabling/Disabling HDL Code for Parame-

# 4.4 Self-testing Code from Samples

Sample parameters generate self-testing code in the test bench. Generally samples will end on a blue signal that is defined with a direction of input. The blue input signals are inputs to the transaction and are driven externally. In the timing diagrams they represent what output the user expects to see from the simulation.

To add samples to the timing diagram, depress the Sample button and use the left and right mouse buttons to add samples (See Section 4.7: Creating New Sample Types).

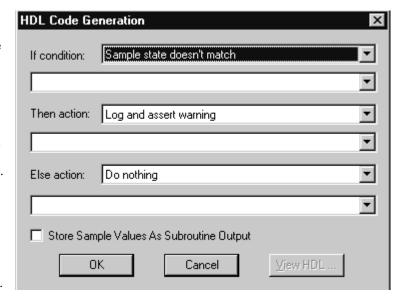

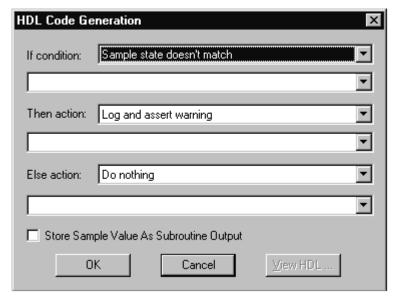

#### To choose the type of HDL code to be generated for a sample:

- Right click the segment of the signal that you want to place the **Sample** on.

- Double left click on the sample name to open the Sample Properties dialog. You can edit the sample window and start time using this dialog.

- Left click on the HDL Code button in the lower left hand side of the dialog. This opens up the HDL Code Generation dialog.

- Choose the type of condition to test for from the **IF Condition** drop down list box.

- Choose the action to take if the condition is true from the **THEN Action** drop down list box.

- Choose the action to take if the condition is false from the **ELSE Action** drop down list box.

- If you want the results of the sample to be exported to the top level module, check the Store Sample Values As Subroutine Output checkbox.

Below each listbox is an edit box that can be used to specify a User-defined action or condition. Section 4.5: Writing User-Defined Samples Conditions and Actions describes this in further detail.

Some of the Sample conditions and actions are as follows:

If conditions:

Sample State doesn't match: indicates that the state within the sample window should match the state that occurs during simulation.

User-defined condition: lets the user enter the exact VHDL or Verilog code for the condition into the edit box below the if conditions drop-down list box.

Actions for then and else blocks:

**Do nothing:** take no action if this branch is executed.

Log and Assert Warning: logs a warning to a file, and also prints a message to the screen.

Assert Warning: prints a message to the screen

End Diagram (set status to Done): Ends execution of this particular timing diagram. The Test Bench will continues to execute as if this timing diagram had normally ended.

Pause Simulation(Verilog only): Stops the entire simulation. Note that this option is not available for VH-DL.

User-defined (action enter below): lets the user directly enter VHDL or Verilog code for the action into the edit box below the action drop-down list box. See Section 4.5: Writing User-Defined Sample Conditions and Actions for more information.

**Note:** The user can add additional sample conditions and actions by editing the sample script. See Section 4.7: Creating New Sample Types.

# 4.5 Writing User-Defined Sample Conditions and Actions

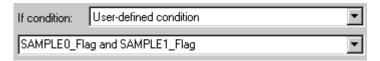

You can add language-specific (e.g. Verilog or VHDL) sample conditions to your diagrams to test for the occurrence of complex events using a User-Defined Condition. Typically this code will access or change the value of signals in the diagram at the sample time, but it is frequently desirable to define a sample condition in terms of previously executed samples. For example, you might wish to execute an action if three different previous samples have all been true. This can be accomplished by writing HDL code that accesses the values of variables which store information about previously executed samples.

User-defined Sample conditions and actions are entered in the HDL Code Generation dialog box with the following steps:

- Select the user-defined option for the Condition, Then Action, or Else Action, using the drop down list box provided.

- Left click in the text box immediately below the option you have set to be user-defined. Note: if you are using a condition or action that you have previously defined, use the drop down feature of this box and select the appropriate option.

- Type in the condition or action that you have defined.

- When you have finished defining/selecting the conditions and actions, close the *HDL Code Generation* Dialog by clicking **OK**.

Two sample variables are automatically generated in a test bench for each sample: a **Boolean variable** that indicates whether the sample condition was true or false and a **sample state variable** that contains the value of the sampled signal at the sample time. The Boolean variable is named as the sample name with \_Flag appended to it and the sample state value is the sample name. For example, a sample named SAMPLE0 would create a Boolean variable named **SAMPLE0 Flag** and a state variable named **SAMPLE0**.

Below is an example of a user-defined sample condition written in VHDL that would cause a sample's then action to execute if three previous samples named SAMPLE0, SAMPLE1, and SAMPLE2 have all been true:

```

SAMPLEO Flag and SAMPLE1 Flag and SAMPLE2 Flag

```

Sample variables can be used in the following places:

- the **condition of the current sample** can reference the sample's *state value variable*. The *Boolean result variable* of the sample cannot be referenced here, because the result of the condition cannot be buried inside the condition.

- actions of the current sample can reference both the sample's *state value* and *Boolean result* variables.

- conditions and actions of samples that occur after the current sample can use either the *state value* or *Boolean result* of the current sample. These are usually triggered from a User-specified action or condition.

**Note:** Sample variables are local to the diagram containing the sample and can only be referenced by HDL code contained in the diagram.

#### **Example**

Assume you have a diagram with three Samples (SAMPLE0, SAMPLE1, and SAMPLE2) where the first two samples test the values of two signals. To make SAMPLE2 true if both SAMPLE0 and SAMPLE1 are true, you would enter the following User-Defined Condition into the edit box below the IF condition:

SAMPLE0\_Flag and SAMPLE1\_Flag are Boolean variables inside the diagram that are given values when their respective Samples execute. Two other variables, SAMPLE0 and SAMPLE1, are also created by TestBencher. These variables hold the value (at the sampling time) of the signals being sampled and can also be used in User-Defined Conditions. For example, to test that the value sampled by SAMPLE0 is equal to the value sampled by SAMPLE1, enter the following User-Defined Condition for SAMPLE2:

**Note:** the types of the signals sampled by SAMPLE0 and SAMPLE1 must be the same, or you will get a type mismatch error when you compile your test bench.

## 4.6 Sample Values as Transaction Outputs

Sample values can be exported from a timing transaction to the top-level test bench. This allows you to add code to the top level test bench that will alter the execution sequence of timing transactions, for instance, based upon the sampled value.

To export a sample value from a timing transaction:

- Double click the sample to be exported. This will open the Sample Properties dialog.

- Click the **HDL Code** button to open the *HDL Code Generation* dialog.

- Check the Store Sample Value as Subroutine Output checkbox.

This will add the port for the sample value to the port list in both the timing transaction code and the top-level test bench. You will be able to reference the sample value signal directly at the top level test bench. The name used to access the value would be of the form:

```

TransactionName SampleName

```

The following example (using the transactions found in Tutorial 5) shows how the sample value could be used to determine whether or not to call a certain transaction:

```

Apply_Tbread ('hF0, 'hAE); // stored sample outputs = Tbread_SAMPLE0

if (Tbread_SAMPLE0 === 'hAE)

Apply Tbwrite ('hF0, 'hAF)

```

# 4.7 Creating New Sample Types

Most of the time you will be using HDL code to specify the actions of Samples. There may, however, be instances when the use of Perl script is preferred. These scripts would define what HDL code is generated for the Sample. This section will explain how to add a user defined Perl script as a Sample type.

There are two steps to adding a new type of action or trigger condition for Samples:

- Adding the Perl subroutine to perform the code generation.

- Adding the subroutine name to TestBencher Pro so that the sample action or condition will be listed in the *Sample HDL* dialog box.

With TestBencher closed, write the Perl condition or action script:

- Open the Sample.pm file.

- Find the comment block that says:

```

Conditional Subroutine : UserDefinedConditionalSubroutine or

Action Subroutine : UserDefinedActionSubroutine

```

- Copy the skeleton subroutine shown below the comment block.

- Rename the subroutine to represent your new sample type.

- Write your new subroutine. The \$hdlCode variable must be set. This string will be the HDL code that is generated for the sample. \$miscInfo is an optional variable that can be used for more code, such as a display or assert statement if desired.

Note: You can always examine the other functions in this file to help write your function.

- Save sample.pm

Next we will add the new condition or action type to the appropriate *HDL Code Generation* dialog drop down menu. Adding the new routine name to TestBencher Pro:

- In TestBencher Pro choose the **Export > Add or Execute Script** menu item to open a dialog of the same name.

- Choose the Conditional or Action radio button in accordance with the type of script you are adding.

- Type the name of the routine into the **Script Name & Command Line** edit box, and type a description into the **Menu Description** edit box.

- Click the **Add** button to add the script.

- Click  $\mathbf{OK}$  to close the dialog box.

# **Chapter 5: Markers**

Markers can be added to timing diagrams to specify specific actions to be taken by the transaction during execution. These actions can include signifying the end of a transaction, creating loops in the transaction, and inserting HDL code calling a subroutine into the transaction.

# 5.1 Adding a Marker to a Diagram

Every marker type provided by TestBencher Pro is placed on the diagram in the same manner. The property settings for the marker are used to specify the different types of markers and the portion of the diagram that the marker is attached to.

#### To place a marker in a diagram:

- Left click the **Maker** button Marker on the Signal Button Bar.