This is an abbreviated datasheet. Contact a Cypress representative for complete specifications. For new designs, please refer to the PALCE22V10.

## PALC22V10B

## Reprogrammable CMOS PAL® Device

## **Features**

- Advanced second generation PAL architecture

- Low power

- 90 mA max. standard

- 100 mA max. military

- CMOS EPROM technology for reprogrammability

- Variable product terms

- −2 x (8 through 16) product terms

- User-programmable macrocell

- Output polarity control

- Individually selectable for registered or combinatorial operation

- "15" commercial and industrial

- $10\;ns\;t_{CO}$

- 10 ns t<sub>S</sub>

- 15 ns t<sub>PD</sub> 50 MHz

- "15" and "20" military

- $10/15 \text{ ns t}_{CO}$

- 10/17 ns ts

- 15/20 ns t<sub>PD</sub>

- 50/31 MHz

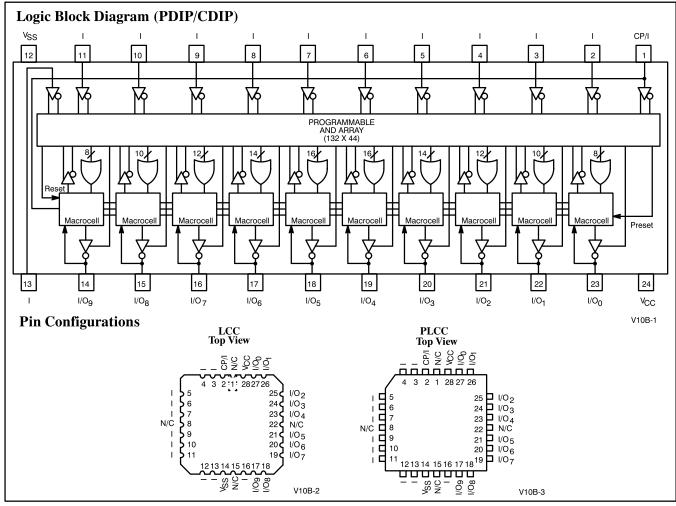

- Up to 22 input terms and 10 outputs

- **Enhanced test features**

- Phantom array

- Top test

- Bottom test

- Preload

- High reliability

- Proven EPROM technology

- 100% programming and functional testing

- Windowed DIP, windowed LCC, DIP, LCC, PLCC available

## **Functional Description**

The Cypress PALC22V10B is a CMOS second-generation programmable logic array device. It is implemented with the familiarsum-of-products(AND-OR)logic structure and a new concept, the "Programmable Macrocell."

The PALC22V10B is executed in a 24-pin 300-mil molded DIP, a 300-mil windowed cerDIP, a 28-lead square ceramic leadless chip carrier, a 28-lead square plastic leaded chip carrier, and provides up to 22 inputs and 10 outputs. When the windowed cer-DIP is exposed to UV light, the 22V10B is erased and can then be reprogrammed. The programmable macrocell provides the capability of defining the architecture of each output individually. Each of the 10 potential outputs may be specified as "registered" or "combinatorial." Polarity of each output may also be individually

PAL is a registered trademark of Advanced Micro Devices

Document #: 38-00195-B