# UltraLogic™ 3.3V High Speed 1K Gate CMOS FPGA

#### **Features**

- Very high speed

- Loadable counter frequencies greater than 80 MHz

- Chip-to-chip operating frequencies up to 60 MHz

- Unparalleled FPGA performance for counters, data path, state machines, arithmetic, and random logic

- Low power

- Standby current typically 250 μA

- 16-bit counter operating at 80 MHz consumes 20 mA

- High usable density

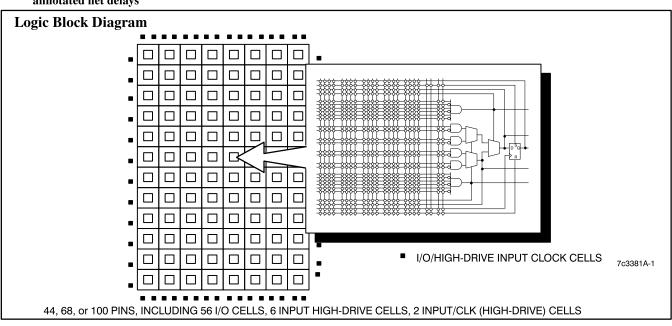

- 8 x 12 array of 96 logic cells provides 3,000 total available gates

- 1,000 typically usable "gate array" gates in 44- and 68-pin PLCC and 100-pin TQFP packages

- Fully PCI compliant inputs and outputs for commercial and industrial temperature range

- Flexible logic cell architecture

- Wide fan-in (up to 14 input gates)

- Multiple outputs in each cell

- Very low cell propagation delay (1.7ns typical)

- Powerful design tools—Warp3<sup>™</sup>

- Designs entered in VHDL, schematics, or both

- Fast, fully automatic place and route

- Waveform simulation with backannotated net delays

- PC and workstation platforms

- Extensive 3rd party tool support

- See Development Systems section

- 5V Tolerant Inputs (see I<sub>IH</sub> spec)

- **Robust routing resources**

- Fully automatic place and route of designs using up to 100 percent of logic resources

- No hand routing required

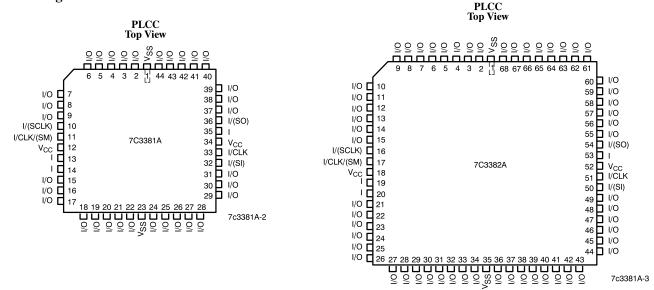

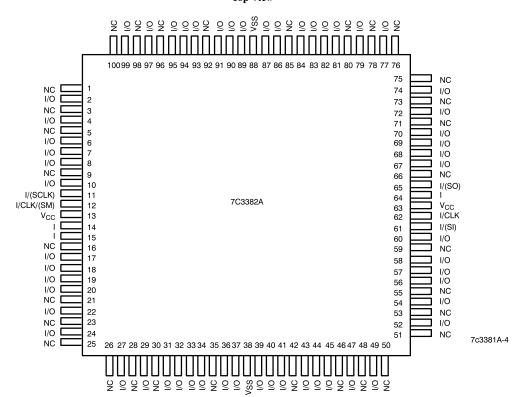

- 32 (CY7C3381A) to 56 (CY7C3382A) bidirectional input/output pins

- 6 dedicated input/high-drive pins

- 2 clock/dedicated input pins with fanout-independent, low-skew nets

- Clock skew < 0.5 ns

- Input hysteresis provides high noise immunity

- Thorough testability at 3.3V

- Built-in scan path permits 100 percent factory testing of logic and I/O cells

- 0.65μ CMOS process with ViaLink™ programming technology

- High-speed metal-to-metal link

- Non-volatile antifuse technology

- 68-pin PLCC is pinout compatible with 2K (CY7C3384A) devices

- 100-pin TQFP is pinout compatible with 3.3V 2K (CY7C3384A) and 4K (CY7C3385A) devices

- Pinout compatible with 5V CY7C381P/2P devices

#### **Functional Description**

The CY7C3381A and CY7C3382A are 3.3V very high speed CMOS user-programmable ASIC (pASIC<sup>™</sup>) devices. The 96 logic cell field-programmable gate array (FPGA) offers 1,000 typically usable "gate array" gates. This is equivalent to 3,000 EPLD or LCA gates. The CY7C3381A is available in a 44-pin PLCC package. The CY7C3382A is available in a 68-pin PLCC and a 100-pin TQFP package.

Low-impedance, metal-to-metal ViaLink interconnect technology provides non-volatile custom logic capable of operating at speeds above 100 MHz. This permits highdensity programmable devices to be used with today's fastest CISC and RISC microprocessors.

Designs are entered into the CY7C3381A and CY7C3382A using Cypress Warp3 software or one of several third-party tools. See the Development Systems section of the Programmable Logic Databook for more tools information.

Warp3 is a sophisticated CAE package that features schematic entry, waveform-based timing simulation, and VHDL design synthesis. The CY7C3381A and CY7C3382A feature ample on-chip routing channels for fast, fully automatic place and route of high gate utilization designs.

For detailed information about the pASIC3380 architecture, see the pASIC380 Family datasheet.

## **Pin Configurations**

## **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

Storage Temperature

| Storage remperature                            |

|------------------------------------------------|

| Ceramic 65°C to +150°C                         |

| Plastic40°C to +125°C                          |

| Lead Temperature                               |

| Supply Voltage $\dots - 0.5V$ to $+7.0V$       |

| Input Voltage $\dots - 0.5V$ to $V_{CC}$ +0.7V |

| ESD Pad Protection                             |

| DC Input Voltage0.5V to 7.0V                   |

|                                                |

##

## **Operating Range**

| Range      | Ambient<br>Temperature | $v_{cc}$        |

|------------|------------------------|-----------------|

| Commercial | 0°C to +70°C           | $3.3V \pm 0.3V$ |

| Industrial | −40°C to +85°C         | $3.3V \pm 0.3V$ |

## **Delay Factor (K)**

| Sneed          | Comm | iercial | Industrial |      |  |

|----------------|------|---------|------------|------|--|

| Speed<br>Grade | Min. | Max.    | Min.       | Max. |  |

| -X             | 0.46 | 3.52    | 0.40       | 3.77 |  |

| -0             | 0.46 | 2.61    | 0.40       | 2.81 |  |

| -1             | 0.46 | 2.23    | 0.40       | 2.39 |  |

## Electrical Characteristics Over the Operating Range

| Parameter         | Description                                 | Test Conditions                           | Min.           | Max.              | Unit |

|-------------------|---------------------------------------------|-------------------------------------------|----------------|-------------------|------|

| V <sub>OH</sub>   | Output HIGH Voltage                         | $I_{OH} = -2.4 \text{ mA}$                | 2.4            |                   | V    |

|                   |                                             | $I_{OH} = -10.0  \mu A$                   | $V_{CC} - 0.1$ |                   | V    |

| V <sub>OL</sub>   | Output LOW Voltage                          | $I_{OL} = 4.0 \text{ mA}$                 |                | 0.4               | V    |

|                   |                                             | $I_{OL} = 10.0 \mu\text{A}$               |                | 0.1               | V    |

| $V_{\mathrm{IH}}$ | Input HIGH Voltage                          |                                           | 2.0            |                   | V    |

| $V_{\mathrm{IL}}$ | Input LOW Voltage                           |                                           |                | 0.8               | V    |

| $I_{IH}$          | Input HIGH Current Sink<br>(For 5V Inputs)  | $5V > V_{\rm IN} > V_{\rm CC}$            |                | 12 <sup>[1]</sup> | mA   |

| I <sub>I</sub>    | Input Leakage Current                       | $V_{IN} = V_{CC}$ or $V_{SS}$             | -10            | +10               | μΑ   |

| $I_{OZ}$          | Output Leakage Current Three-State          | $V_{IN} = V_{CC} \text{ or } V_{SS}$      | -10            | +10               | μΑ   |

| $I_{OS}$          | Output Short Circuit Current <sup>[2]</sup> | $V_{OUT} = V_{SS}$                        | -5             | -50               | mA   |

|                   |                                             | $V_{OUT} = V_{CC}$                        | 5              | 100               | mA   |

| I <sub>CC1</sub>  | Standby Supply Current                      | $V_{IN}$ , $V_{I/O} = V_{CC}$ or $V_{SS}$ |                | 650               | μΑ   |

## Capacitance

| Parameter | Description                      | Test Conditions                                                           | Max. | Unit |

|-----------|----------------------------------|---------------------------------------------------------------------------|------|------|

| $C_{IN}$  | Input Capacitance <sup>[3]</sup> | $T_A = 25^{\circ}\text{C}, f = 1 \text{ MHz}, $<br>$V_{CC} = 3.3\text{V}$ | 10   | pF   |

| $C_{OUT}$ | Output Capacitance               | V CC = 3.3 V                                                              | 10   | pF   |

#### Note

- 1. User must limit input current to 12 mA.

- 2. Only one output at a time. Duration should not exceed 30 seconds.

- 3.  $C_I = 20 \text{ pF max. on I/(SI)}$ .

## Switching Characteristics ( $V_{CC}$ =3.3 V, $T_A$ =25 °C, K=1.00)

|                    |                                    |     | Propagation Delays <sup>[4]</sup><br>with Fanout of |     |     |     |      |  |

|--------------------|------------------------------------|-----|-----------------------------------------------------|-----|-----|-----|------|--|

| Parameter          | Description                        | 1   | 2                                                   | 3   | 4   | 8   | Unit |  |

| LOGIC CELLS        |                                    | -   |                                                     |     |     |     |      |  |

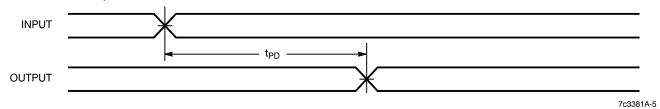

| t <sub>PD</sub>    | Combinatorial Delay <sup>[5]</sup> | 1.7 | 2.1                                                 | 2.7 | 3.3 | 4.8 | ns   |  |

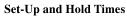

| t <sub>SU</sub>    | Set-Up Time <sup>[5]</sup>         | 2.1 | 2.1                                                 | 2.1 | 2.1 | 2.1 | ns   |  |

| t <sub>H</sub>     | Hold Time                          | 0.0 | 0.0                                                 | 0.0 | 0.0 | 0.0 | ns   |  |

| t <sub>CLK</sub>   | Clock to Q Delay                   | 1.0 | 1.5                                                 | 1.9 | 2.3 | 4.2 | ns   |  |

| t <sub>CWHI</sub>  | Clock HIGH Time                    | 2.0 | 2.0                                                 | 2.0 | 2.0 | 2.0 | ns   |  |

| t <sub>CWLO</sub>  | Clock LOW Time                     | 2.0 | 2.0                                                 | 2.0 | 2.0 | 2.0 | ns   |  |

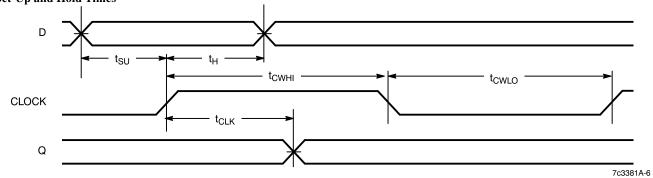

| t <sub>SET</sub>   | Set Delay                          | 1.7 | 2.2                                                 | 2.7 | 3.0 | 4.8 | ns   |  |

| t <sub>RESET</sub> | Reset Delay                        | 1.5 | 1.8                                                 | 2.2 | 2.5 | 3.9 | ns   |  |

| $t_{SW}$           | Set Width                          | 1.9 | 1.9                                                 | 1.9 | 1.9 | 1.9 | ns   |  |

| $t_{RW}$           | Reset Width                        | 1.8 | 1.8                                                 | 1.8 | 1.8 | 1.8 | ns   |  |

|                    |                                       |     | Propagation Delays |     |     |     |     |      |

|--------------------|---------------------------------------|-----|--------------------|-----|-----|-----|-----|------|

| Parameter          | Description                           | 1   | 2                  | 3   | 4   | 6   | 8   | Unit |

| INPUT CELLS        |                                       |     |                    |     |     |     |     |      |

| $t_{IN}$           | Input Delay (HIGH Drive)              | 2.1 | 2.2                | 2.3 | 2.4 | 2.6 | 2.9 | ns   |

| t <sub>INI</sub>   | Input, Inverting Delay (HIGH Drive)   | 2.1 | 2.2                | 2.3 | 2.5 | 2.8 | 3.1 | ns   |

| $t_{\rm IO}$       | Input Delay (Bidirectional Pad)       | 1.4 | 1.8                | 2.2 | 2.6 | 3.4 | 4.2 | ns   |

| t <sub>GCK</sub>   | Clock Buffer Delay <sup>[6]</sup>     | 2.7 | 2.7                | 2.8 | 2.9 | 3.0 |     | ns   |

| t <sub>GCKHI</sub> | Clock Buffer Min. HIGH <sup>[6]</sup> | 2.0 | 2.0                | 2.0 | 2.0 | 2.0 |     | ns   |

| t <sub>GCKLO</sub> | Clock Buffer Min. LOW <sup>[6]</sup>  | 2.0 | 2.0                | 2.0 | 2.0 | 2.0 |     | ns   |

|                    |                                                 | Propagation Delays <sup>[4]</sup> with Output Load Capacitance (pF) of |     |     |     |     |      |

|--------------------|-------------------------------------------------|------------------------------------------------------------------------|-----|-----|-----|-----|------|

| Parameter          | Description                                     | 30                                                                     | 50  | 75  | 100 | 150 | Unit |

| OUTPUT CEI         | LLS                                             |                                                                        |     |     |     |     | _    |

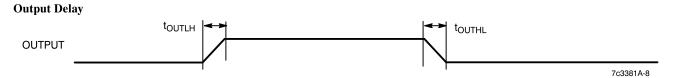

| t <sub>OUTLH</sub> | Output Delay LOW to HIGH                        | 2.7                                                                    | 3.4 | 4.2 | 5.0 | 6.7 | ns   |

| t <sub>OUTHL</sub> | Output Delay HIGH to LOW                        | 2.8                                                                    | 3.7 | 4.7 | 5.6 | 7.6 | ns   |

| t <sub>PZH</sub>   | Output Delay Three-State to HIGH                | 4.0                                                                    | 4.9 | 6.1 | 7.3 | 9.7 | ns   |

| t <sub>PZL</sub>   | Output Delay Three-State to LOW                 | 3.6                                                                    | 4.2 | 5.0 | 5.8 | 7.3 | ns   |

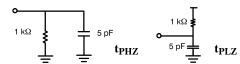

| t <sub>PHZ</sub>   | Output Delay HIGH to Three-State <sup>[7]</sup> | 2.9                                                                    |     |     |     |     | ns   |

| $t_{PLZ}$          | Output Delay LOW to Three-State <sup>[7]</sup>  | 3.3                                                                    |     |     |     |     | ns   |

- Notes:

4. Worst-case propagation delay times over process variation at V<sub>CC</sub> = 3.3V and T<sub>A</sub> = 25°C. Multiply by the appropriate delay factor, K, for speed grade to get worst-case parameters over full V<sub>CC</sub> and temperature as a specified in the operating range. All inputs are TTL with ture range as specified in the operating range. All inputs are TTL with 3-ns linear transition time between 0 and 3 volts.

- These limits are derived from worst-case values for a representative selection of the slowest paths through the pASIC380 logic cell including net delays. Guaranteed delay values for specific paths should be determined from simulation results.

- Clock buffer fanout refers to the maximum number of flip-flops per half column. The number of half columns used does not affect clock buffer delay.

- 7. The following loads are used for  $t_{PXZ}$ :

## **High Drive Buffer**

|                  |                                   | # High Drives<br>Wired | Propagation Delays $^{[4]}$ with Fanout of |     | ıt of |     |     |      |

|------------------|-----------------------------------|------------------------|--------------------------------------------|-----|-------|-----|-----|------|

| Parameter        | Description                       | Together               | 12                                         | 24  | 48    | 72  | 96  | Unit |

| t <sub>IN</sub>  | High Drive Input Delay            | 1                      | 4.0                                        | 4.9 |       |     |     | ns   |

|                  |                                   | 2                      |                                            | 3.5 | 5.0   |     |     | ns   |

|                  |                                   | 3                      |                                            |     | 4.0   | 4.8 | 5.6 | ns   |

|                  |                                   | 4                      |                                            |     |       | 4.1 | 4.8 | ns   |

| t <sub>INI</sub> | High Drive Input, Inverting Delay | 1                      | 4.2                                        | 5.1 |       |     |     | ns   |

|                  |                                   | 2                      |                                            | 3.7 | 5.2   |     |     | ns   |

|                  |                                   | 3                      |                                            |     | 4.2   | 5.0 | 5.8 | ns   |

|                  |                                   | 4                      |                                            |     |       | 4.3 | 5.0 | ns   |

## **Switching Waveforms**

### **Combinatorial Delay**

## Switching Waveforms (continued)

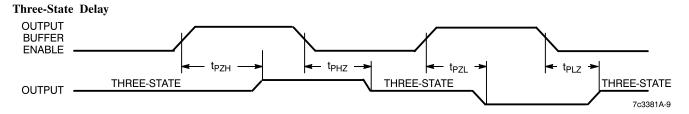

## **Typical AC Characteristics**

Propagation delays depend on routing, fan-out, load capacitance, supply voltage, junction temperature, and process variation. The AC Characteristics are a design guide to provide initial timing estimates at nominal conditions. Worst-case estimates are obtained when nominal propagation delays are multiplied by the appropri-

ate Delay Factor, K, as specified by the speed grade in the Delay Factor table. The effects of voltage and temperature variation are illustrated in the graphs below. The *Warp3* Delay Modeler extracts specific timing parameters for precise simulation results following place and route.

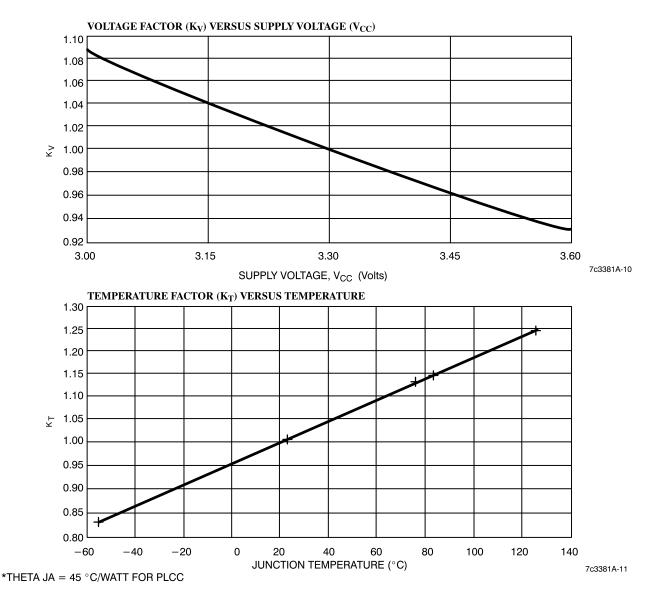

## **Combinatorial Delay Example** (Load = 30 pF, K=1, Fanout=1)

INPUT DELAY + COMBINATORIAL DELAY + OUTPUT DELAY = 5.9 ns

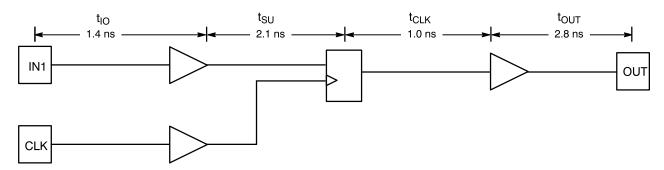

## **Sequential Delay Example** (Load = 30 pF, K=1, Fanout=1)

INPUT DELAY + REG SET-UP + CLOCK TO Q DELAY + OUTPUT DELAY = 7.3 ns

## **Ordering Information**

| Speed<br>Grade | Ordering Code | Package<br>Name | Package Type                        | Operating<br>Range |

|----------------|---------------|-----------------|-------------------------------------|--------------------|

| 1              | CY7C3381A-1JC | J67             | 44-Lead Plastic Leaded Chip Carrier | Commercial         |

|                | CY7C3381A-1JI | J67             | 44-Lead Plastic Leaded Chip Carrier | Industrial         |

| 0              | CY7C3381A-0JC | J67             | 44-Lead Plastic Leaded Chip Carrier | Commercial         |

|                | CY7C3381A-0JI | J67             | 44-Lead Plastic Leaded Chip Carrier | Industrial         |

| X              | CY7C3381A-XJC | J67             | 44-Lead Plastic Leaded Chip Carrier | Commercial         |

|                | CY7C3381A-XJI | J67             | 44-Lead Plastic Leaded Chip Carrier | Industrial         |

| Speed<br>Grade | Ordering Code | Package<br>Name | Package Type                        | Operating<br>Range |

|----------------|---------------|-----------------|-------------------------------------|--------------------|

| 1              | CY7C3382A-1AC | A100            | 100-Pin Thin Quad Flat Pack         | Commercial         |

|                | CY7C3382A-1JC | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |

|                | CY7C3382A-1AI | A100            | 100-Pin Thin Quad Flat Pack         | Industrial         |

|                | CY7C3382A-1JI | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |

| 0              | CY7C3382A-0AC | A100            | 100-Pin Thin Quad Flat Pack         | Commercial         |

|                | CY7C3382A-0JC | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |

|                | CY7C3382A-0AI | A100            | 100-Pin Thin Quad Flat Pack         | Industrial         |

|                | CY7C3382A-0JI | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |

| X              | CY7C3382A-XAC | A100            | 100-Pin Thin Quad Flat Pack         | Commercial         |

|                | CY7C3382A-XJC | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |

|                | CY7C3382A-XAI | A100            | 100-Pin Thin Quad Flat Pack         | Industrial         |

|                | CY7C3382A-XJI | J81             | 68-Lead Plastic Leaded Chip Carrier |                    |

ViaLink and pASIC are trademarks of QuickLogic Corporation. *Warp3* and UltraLogic are trademarks of Cypress Semiconductor Corporation.

Document #: 38-00252-B

## **Package Diagrams**

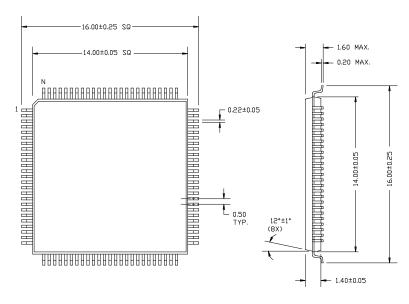

#### 100-Pin Thin Quad Flat Pack A100

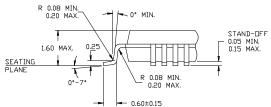

## 44-Lead Plastic Leaded Chip Carrier J67

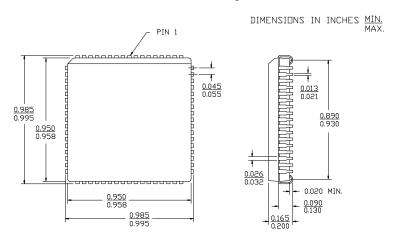

## Package Diagrams (continued)

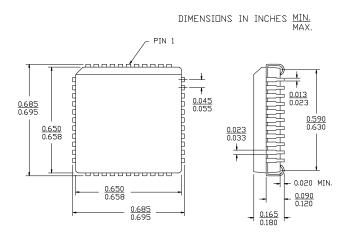

#### 68-Lead Plastic Leaded Chip Carrier J81

<sup>©</sup> Cypress Semiconductor Corporation, 1995. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor Corporation product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems applications implies that the manufacturer assumes all risk of such use and in so doing indemnifies Cypress Semiconductor against all damages.