## ADVANCED INFORMATION Ultra39448

## UltraLogic<sup>™</sup> 448-Macrocell CPLD

## **Features**

- 448 macrocells in 28 logic blocks

- In-System Reprogrammable (ISR™)

- Fully PCI compliant

- Full JTAG compatibility

- 3.3V or 5V operation

- Programmable speed/power options

- 192 or 224 I/O pins

- 4 dedicated inputs/clocks

- No hidden delays

- High speed

- $-f_{MAX} = 100 \text{ MHz}$

- $-t_{PD} = 12 \text{ ns}$

- $-t_{\rm S} = 6 \, \rm ns$

- $-t_{CO} = 6.5 \text{ ns}$

- Available in 240-pin and 304-pin PQFP packages

- Pin compatible with the Ultra39384 and Ultra39512

## **Functional Description**

The Ultra39448 is a high-density, high-performance Complex Programmable Logic Device (CPLD) providing in-system reprogrammability (ISR) and full Joint Test Action Group (JTAG IEEE1149.1) compatibility. It is part of the Ultra39000™ family of fast, reconfigurable CPLDs, which have been designed to bring the high performance and the ease of use of 22V10s to ultra high-density PLDs. The entire family is also fully compliant with the PCI Local Bus Specification and will operate at either 3.3V or 5V.

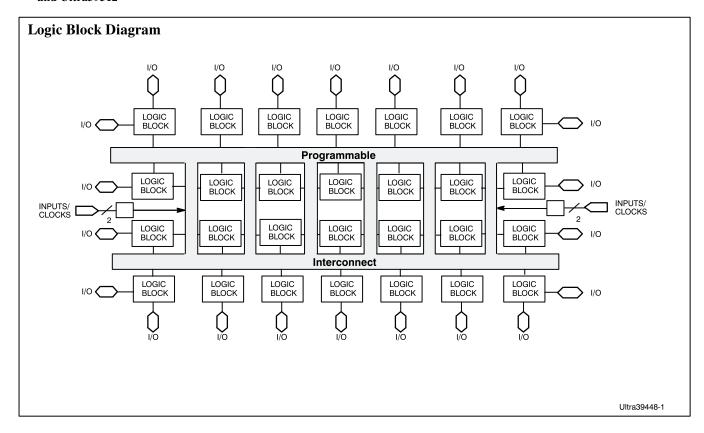

The 448 macrocells in the Ultra39448 are divided between 28 logic blocks. Each logic block contains 16 macrocells along with a product term array and a fast, intelligent product term matrix. Each logic block in the Ultra39000 architecture is connected through a Programmable Interconnect

that produces extremely fast and predictable paths through the device.

All members of the Ultra39000 family feature an abundant number of I/O resources. The Ultra39448 contains either 192 or 224 I/O pins as well as four dedicated inputs/clocks and provides both fast synchronous and asynchronous clocking capabilities.

Additionally, the Ultra39448 features a programmable speed/power option that allows users to optimize designs for either ultra-fast performance or ultra-low power. The family also provides slew rate control for each of the outputs, which reduces switching noise. And finally, the Ultra39448 features a very simple timing model that results in parameters that are not dependent on the device resources utilized or the type of application being implemented.

UltraLogic, ISR, and Ultra39000 are trademarks of Cypress Semiconductor Corporation

Document #: 38-00469

<sup>©</sup> Cypress Semiconductor Corporation, 1995. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor Corporation product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems applications implies that the manufacturer assumes all risk of such use and in so doing indemnifies Cypress Semiconductor against all damages.