# High Speed Multiplier Using Vedic Mathematics Technique

Omanand M. Wakpanjar Electronics engineering, Wardha <u>omanand1989@gmail.com</u>

Suraj A. Dafe Electronics engineering,Wardha surajdafe@gmail.com Lokesh M. Bhalme Electronics engineering,Wardha <u>Bhalame.lokesh1@gmail.com</u>

Suraj A. Bhagat Electronics engineering,Wardha Surajbhagat82@gmail.com Swapnil I. Rakhunde Electronics engineering Wardha <u>rakhundeswapnil@gmail.com</u>

Suraj P. Bhagat Electronics engineering,Wardha surajbhagat3@gmail.com

Abstract - The demand for the high speed at the time of process which undergoes in less time as fast as possible. A multiplier is needed due to its high speed processing ability. A multiplier is a major source of power dissipation and high delay. The delay can be reduced using Vedic multiplying by techniques .So which technique of Vedic multiplier used in the process so the delay is minimum. In our project we are using 4x4 bit Vedic Multiplier which consist vertical and crosswise methods. This process is done by using Xilinx software. And this process seems to have high performance in terms of speed.

**Keywords**: - Vedic multiplication, Half Adder, Full Adder, VHDL, hardware design.

## **1. INTRODUCTION**

In the past, the parameters like high speed, small area and low cost where the major areas of concern, whereas power consideration are now gaining the attention of the scientific community associated the VLSI design. With the advance technology demand for high speed and portable digital signal processing system is increased. Multiplier is extensively used in digital signal processing due to its fastest growing technology. Now a day digital signal processing is present in every technical field. DSP helps to do fastest multiplication and addition operations.

The ancient system of Vedic mathematics was rediscovered from the Vedas between the year 1911 and 1918 by Sri Bharati Krishna Tirthaji. This technique is totally based on 16 sutras in this paper we will discuss the architecture based on Urdhava tirvakbhyamin which vertically and crosswise mathematical operation is performed according to the sutra is presented. the paper presents the basic logic for 4x4 multiplier and the implementation of it with less hardware used. Multiplication having wide application in different areas of engineering technology and in digital systems booths algorithm and array algorithm are the most successful

Algorithm use for multiplication operations and the other methods include Vedic multipliers based on "urdhva tiryakbhyam".

Digital multipliers are the most commonly used components in any digital circuit design. They are very fast and efficient components that are used to implement. Based upon the arrangement of the modules, there are various types of multipliers exists. Suitable multiplier architecture is chosen for this application.

The Vedic mathematics is very simple, regular as well as logical. Its high degree of eminence is attributed to the aforementioned facts. It is these phenomenal characteristics, which made Vedic mathematics, become so popular and thus it has become one of the leading topics of research not only in India but abroad as well. Vedic mathematics' logics and steps can be directly applied to problems involving trigonometric functions, plane and sphere geometry, differential calculus, integral calculus and applied mathematics of various kind.

#### 2. VEDIC MULTIPLICATION

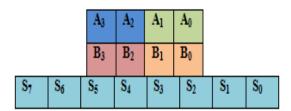

The proposed Vedic Multiplier is Tiryakbhyam" based on''Urdhva Sutra have Sutra(algorithm).These been traditionally used for the multiplication of two numbers in the decimal number system. In this work, we apply the same ideas to the binary number system to make the proposed with the algorithm compatible digital hardware. Its general multiplication formula applicable to all cases of multiplication. It means vertical and crosswise. It is based on novel concept through which the generation of all partial products can be done with concern addition of this partial products. Multiplier consist of 4 inputsand its resultant output is of 8-bits.If the input is of maximum n-number of bits than its resultant output by multiplication is of maximum 2n-bits. The A3, A2, A1, A0 and B3,B2,B1,B0 are the two inputs taken in 4X4 multiplier.

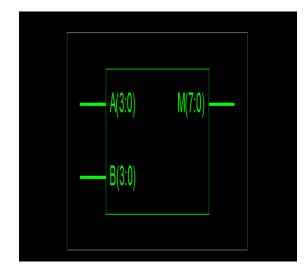

Fig-1. 4 bit Vedic multiplier

# THE VEDIC SUTRAS WITH THEIR MEANINGS ARE

LISTED BELOW:

There are 16 Vedic sutras which are listed below with their meanings.

1. (Anurupye) Shunyamanyat –One of them is in ratio then other value is in ratio.

2. ChalanaKalanabyham -Differences and Similarities

3. EkadhikinaPurvena- The value is more than the previous one.

4. EkanyunenaPurvena – The value is less than the previous one.

5. Gunakasamuchyah-The factors of sum is equal to sum of factor.

6. Gunitasamuchyah-the product of sum is equal to sum of product.

7. NikhilamNavatashcaramamDashatah -The value from 9 and last from 10.

8. ParaavartyaYojayet-Transpose and adjust the values.

9. Puranapuranabyham - completion or noncompletion.

10. Sankalana- vyavakalanabhyam -By addition and by subtraction.

11. ShesanyankenaCharamena- The remainders by the last digit.

12. ShunyamSaamyasamuccaye -When the sum is equal then its sum is zero.

13. Sopaantyadvayamantyam -The ultimate and twice the penultimate.

14. Urdhva-tiryakbhyam -It performs vertically and crosswise operations.

15. Vyashtisamanstih -Part and Whole.

16. Yaavadunam- Whatever the extent of its deficiency.

This all are the 16 Vedic sutras. The Vedic multiplication technique is based on sutra named one of the as'Urdhvatiryakbhyam'. The vertical product of bit A0 & B0 gives the output S0.The sum A0.B0 &A1.B0 gives the output S1 which is 10 bit of its previous sum S0.And the remaining multiplication done is with same method. The position of ten's and hundred bit are forward carry to the next addition performed. From the 10's bit S6 the answer of S7 bit will come in the multiplication process. The multiplication process is shown in figure with different architectures.

#### **3. URDHVA TIRYAKBHYAM SUTRA**

Urdhva Triyakabhyam (vertical and crosswise) algorithm can be generalized for n x n bit number. This multiplier has the advantage that has the number increases, gate delay and area increases very slowly as compare to other multiplier. It is very efficient to time space and power .this architecture is demonstrated in the terms of silicon area or speed. Since the partial product .The multiplier has greater advantage that the no. And their sum is calculated in parallel and crosswise method, since the multiplier required same amount of time to calculate the product the multiplier is independent of clock frequency of the processor. By adopting the Vedic Multiplier, structure ,due to its regular structure, It can be easily layout in microprocessors and designers can easily

circumvent this power of multiplier it can be easily be increased by increasing the input and output data bus widths since it has quite a regular problems to avoid catastrophic device faliour. The net advantage is that it reduces the need of microprocessor to operate at increasingly high clock frequencies.While at higher clock frequency generally results in increased processing power. Its only disadvantage is that power dissipation increases which result in higher device operating temperature.

#### **4. ADDER STRUCTURE**

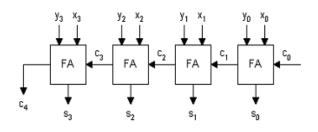

In this paper we use four bit full adder to implement the Vedic multiplier.

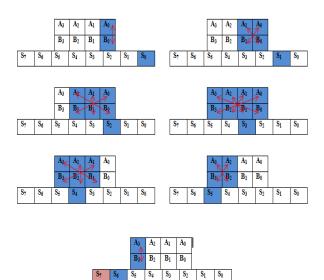

Four bit full adder- Four bit full adder consist of multiple full adder with carry ins and carry out chains together, where the carry bit ripples from 1 bit to the next bit .All four full adder are internally connected to each other. Whereas each full adder supplied with two inputs.

Fig-2. Four bit full adder

The two Boolean functions for the sum and carry are:

$SUM = Ai \bigoplus Bi \bigoplus Ci$ Cout= Ci+1 = Ai · Bi + (Ai \bigoplus Bi) · Ci

#### 5. BLOCK IMPLEMENTATION OF 4X4 VEDIC MULTIPLIER

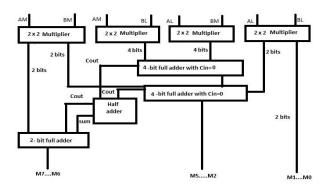

The implementation of 4x4 Vedic multiplier using "Urdhva Tiryakbhyam" sutra is shown in the fig-4. The 4x4 multiplier is pring Technology Trends in Engineering

SPARK'15- XI<sup>th</sup> National Conference on Engineering Technology Trends in Engineering

implemented using four 2x2 Vedic multiplier modules, 2 four bit full adders and half adder .Each 2 x2 multiplier consist of two inputs which are internally connected to each other. For the design of 4x4 block the first step is to grouping the two bit of each four bit input. This group in pair will form vertical and crosswise product. The partial product shown represent the vertical and crosswise product terms.

Fig-4. Block diagram of 4bit Urdhva multiplier with 4 bit full adder

## 6. SIMULATION OF 4X4 MULTIPLIER

Fig.6:- block view of 4bit Urdhva Multiplier

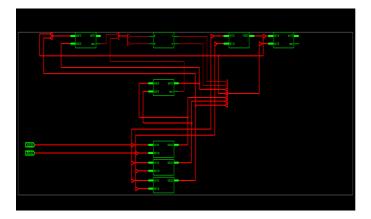

Fig.7:- RTL view 4bit Urdhva multiplier

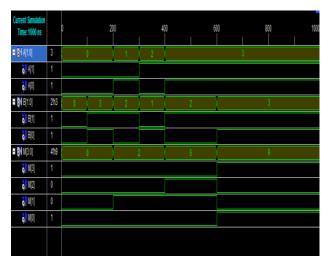

Fig.8:-simulation result of 4bit multiplier

## 7. RESULT ANALYSIS

| Types of multiplier<br>(4 bit)                  | Delay(ns) |

|-------------------------------------------------|-----------|

| Urdhva multiplier<br>with ripple carry<br>adder | 16.236    |

| Traditional booth multiplier                    | 25.52ns   |

Table 1:- comparison of multiplier in the terms of delays

This paper shows the comparison between 4bit multiplier with ripple carry adder, half adder,two bit adder Uradhvatiryakbhyam sutra the coding of 4x4 multiplier is done in VHDL, and it is synthesized and simulated using Xilinx ISE14.2.Software.

The result shows that 4x4 Vedic multiplier with ripple carry adder having less delay or we conclude that 4x4 Vedic multiplier is faster than 4bit traditional booths multiplier. And it acquire less area on the circuit and it take less power as compare to any other multiplier.

# **8.CONCLUSION**

The high speed multiplier is used to design efficient full adders such as high performance and less delay significantly achieves high optimization. the efficient full adder design is implant in Vedic multiplier. Array and booth multiplier are not efficient than Vedic multiplier.Hence Urdhava Tiryakbhyam multiplier is the best multiplier compared to booth multiplier when compared to delay and power calculations.

#### 9. REFERENCES

[1] Jagadguru Swami, Sri Bharati Krisna, Tirthaji Maharaja, "Vedic Mathematics or Sixteen Simple Mathematical Formulae from the Veda, Delhi (1965)", Motilal Banarsidas, Varanasi, India, 1986.

[2]Pushpalata Verma, K. K. Mehta International Journal of Engineering and Advanced Technology (IJEAT) ISSN: 2249 – 8958, Volume-1, Issue-5, June 2012

[3]H. Thapliyal and H.R Arbania. "A Time-Area-Power Efficient Multiplier and Square SPARK'15- XI<sup>th</sup> National Conference on Engineering Technology Trends in Engineering

Architecture Based On Ancient Indian Vedic Mathematics", Proceedings of the 2004 International Conference on VLSI (VLSI'04), Las Vegas, Nevada, June 2004, pp. 434-439.

[4] Thapliyal H. and Srinivas M.B, "High Speed Efficient NxN Bit Parallel Hierarchical Overlay Multiplier Architecture Based on Ancient Indian Vedic Mathematics", Transactions on Engineering

[5] P. D. Chidgupkar and M. T. Karad, "The Implementation of Vedic Algorithms in Digital Signal Processing", Global J. of Engg. Edu, Vol.8, No.2, 2004, UICEE Published in Australia

[6] Thapliyal H. and Srinivas M.B, "High Speed Efficient NxN Bit Parallel Hierarchical Overlay Multiplier Architecture Based on Ancient Indian Vedic Mathematics", Transactions on Engineering, Computing and Technology, 2004, Vol.2.

[7] Harpreet Singh Dhillon and Abhijit Mitra, "A Reduced– Bit Multipliction Algorithm for Digital Arithmetics", International Journal of Computational and Mathematical Sciences 2.2 @ www.waset.orgSpring2008.

[8] Honey Durga Tiwari, Ganzorig Gankhuyag, Chan Mo Kim and Yong Beom Cho, "Multiplier design based on ancient Indian Vedic Mathematician", International SoC Design Conference, pp. 65- 68, 2008.